佑華微電子股份有限公司

# AM8EB051A Data Sheet

新竹市光復路二段295號9樓之1號 電話: 03-573 6660 傳真: 03-573 6661 <u>www.ealpha.com.tw</u>

# Alpha Microelectronics Corp.

9F-1, 295, Sec. 2, Kuang Fu Rd., Hsinchu, Taiwan Tel : +886-3-573 6660 Fax: +886-3-573 6661 www.ealpha.com.tw

# **Revision History**

| Rev | Date     | Description | Page |

|-----|----------|-------------|------|

| 1.0 | 2006/3/9 | Original.   | -    |

# Table of Content

| 1. Gene   | eral Description                                                  | 4  |

|-----------|-------------------------------------------------------------------|----|

| 1.1       | Features                                                          | 4  |

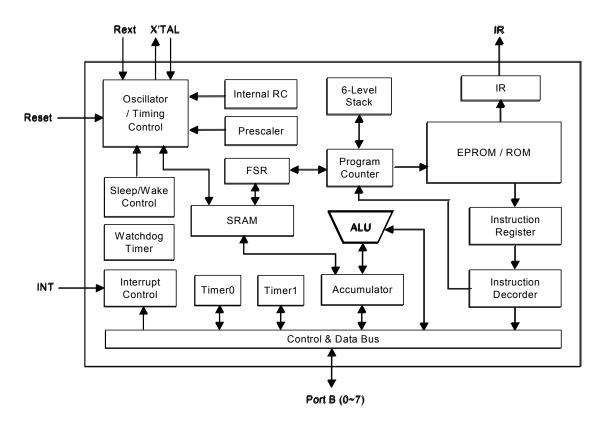

| 1.2       | Block Diagram                                                     | 5  |

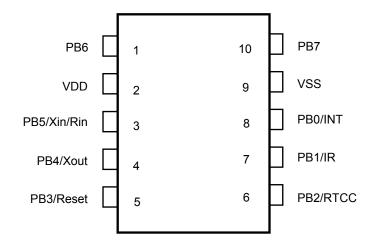

| 1.3       | Pin Assignment                                                    | 5  |

| 1.4       | Pin Description                                                   | 6  |

| 2. Mem    | ory Organization                                                  | 7  |

| 2.1       | Program Memory Organization                                       | 7  |

| 2.2       | Data Memory Map                                                   | 8  |

| 3. Func   | tional Descriptions                                               | 9  |

| 3.1       | General Function Registers                                        | 9  |

| 3.2       | I/O Control Registers (Addressed by IOST, IOSTR instruction)      |    |

| 3.3       | Special Function Registers (Addressed by SFUN, SFUNR instruction) |    |

| 3.4       | RESET                                                             |    |

| 3.5       | I/O Ports                                                         |    |

| 3.6       | Real Time Clock (TIMER0) And Watchdog Timer                       |    |

| 3.7       | Oscillator Configuration                                          | 21 |

| 3.8       | Interrupts                                                        | 24 |

| 3.9       | Power-Down Mode (Sleep)                                           | 25 |

| 3.10      | Configuration Word                                                |    |

| 4. Instru | uction Set                                                        | 27 |

| 5. Elect  | rical Characteristics                                             |    |

| 5.1       | Absolute Maximum Rating                                           |    |

| 5.2       | DC Characteristics (Top = 25°C)                                   |    |

| 6. Orde   | ring Information                                                  | 42 |

# 1. General Description

The AM8EB051A is a family of low-cost, high speed, high noise immunity and EPROM-embedded 8-bit CMOS micro-controllers. It employs a RISC architecture with only 55 instructions. All instructions are single cycle except for program branches that take two cycles. The AM8EB051A provides powerful and easy useful instruction sets that can directly or indirectly address its register files and data memory.

# 1.1 Features

- Wide operating voltage range: 2.0 ~ 5.5V at 32kHz, 2.2 ~ 5.5V at DC-4MHz, 2.6 ~ 5.5V at DC-20MHz.

- Wide operating frequency range: 32kHz ~ 20MHz.

- Wide operating temperature range: -40°C ~ 85°C.

- ROM: 1K x 14 bits.

- RAM: 48 x 8 bits.

- Selectable oscillator options:

- IRC: Internal Resistor and Capacitor Oscillator.

- EXT-R: External Resistor and internal Capacitor Oscillator.

- ERC: External Resistor and Capacitor Oscillator.

- LF-XTAL: Low Frequency Crystal Oscillator.

- XTAL: Crystal/Resonator Oscillator.

- HF-XTAL: High Frequency Crystal/Resonator Oscillator.

- 6-level deep hardware stack.

- Total 55 single word instructions.

- All instructions are single cycle except for program branches which are two-cycle.

- Direct, indirect addressing modes for data accessing.

- All ROM area LGOTO instruction, all ROM area subroutine LCALL instruction.

- 8-bit real time clock/counter (Timer0) with 8-bit programmable prescaler.

- On chip Watchdog Timer (WDT) with internal oscillator for reliable operation and software Watchdog enable/disable control.

- Internal Power-on Reset (POR).

- Built-in Low Voltage Reset (LVR).

- Power-up Reset Timer (PWRT) and Oscillator Start-up Timer (OST).

- SLEEP mode function to reduce power consumption.

- I/O ports PB with independent direction control.

- Software I/O pull-high/pull-down or open-drain control.

- One IR carrier output (38k / 57kHz).

- Four Interrupt source:

- Timer0 overflow.

- PB input change.

- External Interrupt Pin.

- Watchdog time out Interrupt. (If this function is enabled by programming the configuration word.)

- Wake-up from SLEEP by external INT pin, Port B input change, WDT reset or WDT interrupt.

- Programmable Code Protection.

# 1.2 Block Diagram

# 1.3 Pin Assignment

| 2 VDD         | 1<br>PB6 |            |

|---------------|----------|------------|

| 3 PB5/Xin/Rin | 1.50     |            |

| 4 PB4/Xout    |          | РВ7 10     |

| 5 PB3/Reset   |          | vss 9      |

|               |          | PBO/INT 8  |

|               |          | PB1/IR 7   |

|               |          | PB2/RTCC 6 |

# 1.4 Pin Description

| Name        | ATTR. | Function                                                                |

|-------------|-------|-------------------------------------------------------------------------|

| PB0/INT     | I/O   | Bi-directional PB0.                                                     |

| P BO/INT    | 1/0   | External interrupt input.                                               |

| PB1/IR      | I/O   | Bi-directional PB1.                                                     |

|             | 1/0   | IR carrier output.                                                      |

| PB2/RTCC    | I/O   | Bi-directional PB2                                                      |

|             |       | Input pin of real time counter/clock.                                   |

| PB3/Reset   | I/O   | Bi-directional PB3.                                                     |

|             |       | Input pin for device reset. If this pin is low, the device is reset.    |

|             |       | X'TAL type: Output terminal of crystal oscillator.                      |

| PB4/Xout    | I/O   | EXT-R or ERC type: This pin can output instruction clock.               |

|             |       | IRC type: Bi-directional PB4, or this pin can output instruction clock. |

|             |       | X'TAL type: Input terminal of crystal oscillator.                       |

| PB5/Xin/Rin | I/O   | EXT-R type: External resistor for EXT-R oscillator;                     |

|             |       | ERC type: Input pin of external RC oscillator.                          |

|             |       | IRC type: Bi-directional PB5.                                           |

| PB6         | I/O   | Bi-directional PB6.                                                     |

| PB7         | I/O   | Bi-directional PB7.                                                     |

| VDD         | -     | Power supply.                                                           |

| VSS         | -     | Ground.                                                                 |

# 2. Memory Organization

AM8EB051A memory is organized into program memory and data memory.

# 2.1 Program Memory Organization

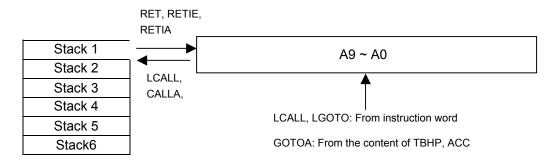

The AM8EB051A has a 10-bit Program Counter (PC) capable of addressing a 1K×14 bit program memory space. The RESET vector of the AM8EB051A is at 000h; The INT instruction software interrupt vector is at 001h; The Global hardware interrupt vector is at 008h. AM8EB051A supports all ROM area LCALL/LGOTO instructions without page.

# PC $\langle$ 9:0 $\rangle$ STACK Level 1 STACK Level 2 STACK Level 3 STACK Level 4 STACK Level 5 STACK Level 6 3FFh Global H/W Interrupt 008h S/W Interrupt Vector 001h **Reset Vector** 000h

# FIGURE 2.1: Program Memory Map and STACK

# 2.2 Data Memory Map

Data memory includes General Function Registers and General Storage Registers. The Data Memory are accessed either directly or indirectly through the FSR register.

| Address   | Description                  |

|-----------|------------------------------|

| 00h       | Indirect Addressing Register |

| 01h       | Timer0                       |

| 02h       | PCL                          |

| 03h       | STATUS                       |

| 04h       | FSR                          |

| 06h       | PortB                        |

| 0Fh       | Interrupt Status Register    |

| 10h ~ 3Fh | General Storage Register     |

TABLE 2.1: Registers File Map for AM8EB051A

# 3. Functional Descriptions

# 3.1 General Function Registers

# • INAR (Indirect Address Register): R0

R0 is not a physically implemented register. It is used as an indirect addressing pointer. Any instruction accessing this register can access data pointed by FSR(R4).

# • Timer0 (8-bit real-time clock/timer): R1

This register increases by an external signal edge applied to RTCC pin, or by internal instruction cycle. It can be read or written as any other register.

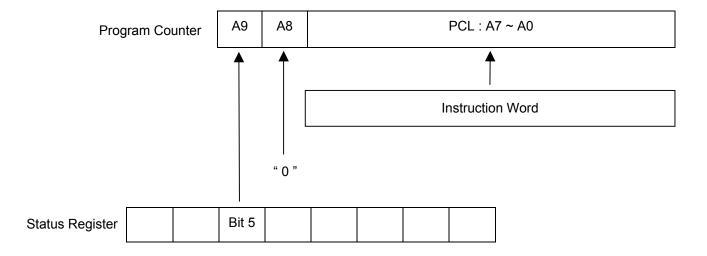

# • PCL (Low Byte of Program Counter): R2

This register increases itself every instruction cycle, except the following condition shown in Figure below.

For change content of PCL register instruction where the PCL register is the destination, the Bit5 of the Status register will provide data to A9 of the Program Counter, The A8 of the Program Counter is always cleared. The configuration is shown in following figure .

# • STATUS (Status Register): R3

The content of R3 is listed in Table below.

# **TABLE 3.1: STATUS Register**

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                            |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | С      | Carry/borrow bit<br>ADD = 1, A carry occurred<br>= 0, A carry did not occur<br>SUB = 1, A borrow did not occur<br>= 0, A borrow occur                                                                                                                                                                                  |

| 1   | DC     | Half carry/half borrow bit<br>ADD = 1, A carry from the 4th low order bit of the result occurred<br>= 0, A carry from the 4th low order bit of the result did not occur<br>SUB = 1, A borrow from the 4th low order bit of the result did not occur<br>= 0, A borrow from the 4th low order bit of the result occurred |

| 2   | Z      | Zero bit = 1, The result of a logic operation is zero<br>= 0, The result of a logic operation is not zero                                                                                                                                                                                                              |

| 3   | PD     | Power down flag bit = 1, After power-up or by the CLRWDT instruction<br>= 0, By the SLEEP instruction                                                                                                                                                                                                                  |

| 4   | то     | Time overflow flag bit = 1, After power-up or by the CLRWDT or SLEEP instruction<br>= 0, A WDT time-overflow occurred                                                                                                                                                                                                  |

| 5   | PA0    | Program Page Pre-select Bit<br>PA0 = 0, Program Page 0 ( 000h ~ 1FFh )<br>PA0 = 1, Program Page 1 ( 200h ~ 3FFh )                                                                                                                                                                                                      |

| 6   | -      | General purpose R/W bits                                                                                                                                                                                                                                                                                               |

| 7   | RST    | =1, Wake-up from sleep mode by Port B input change interrupt.                                                                                                                                                                                                                                                          |

# • FSR (File select register pointer): R4

Bit 0~5 are used to select up to 64 registers (address: 00h~3Fh) in the indirect addressing mode; Bit 6~7 are not used and always read "1" shown in following Figure,

| 1         | 1                         | B5 | B4 | B3       | B2     | B1        | B0        | ]                  |

|-----------|---------------------------|----|----|----------|--------|-----------|-----------|--------------------|

|           |                           |    |    |          |        |           |           |                    |

| 00h       | INAR                      |    |    |          |        |           |           |                    |

| 01h       | Timer0                    |    |    |          | Indire | ect Addre | ssing Mod | le location select |

| 02h       | PCL                       |    |    |          |        |           |           |                    |

| 03h       | STATU                     | IS |    |          |        |           |           |                    |

| 04h       | FSR                       |    |    | <b>▲</b> | ļ      |           |           |                    |

| 06h       | PortB                     |    |    |          |        |           |           |                    |

| 0Fh       | Interrupt Status Register |    |    |          |        |           |           |                    |

| 10h ~ 3Fh | SRAM                      |    |    |          |        |           |           |                    |

# • PORT B: R6

PB7:PB0, bi-directional I/O Register.

# • Interrupt Status Register: RF

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | WDTIF |       |       |       | EXIF  | PBIF  | TOIF  |

\* Bit 0 (T0IF) : Timer0 overflow interrupt flag. Set "1" when the Timer0 overflow, reset by software.

\* Bit 1 (PBIF) : PortB input change interrupt flag. Set "1" when PortB input change, reset by software.

\* Bit 2 (EXIF) : External INT pin interrupt flag. Set "1" when External INT pin interrupt, reset by software.

\* Bit 3 ~ 5 : Not used.

\* Bit 6 (WDTIF) : Watchdog timer out interrupt flag. Set "1" when watchdog time out interrupt, reset by software.

\* Bit 7 : Not used.

# • R10 ~ R3F

R10 ~ R3F are general storage registers.

# • TOMODE REGISTER

TOMODE is a readable / writable register and the content is listed in following Table.

| Bit | Symbol  |                                                                                                                                            | De                                                                                                                                                                          | scription                                                                 |                                                                             |  |  |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

|     |         | Bit value                                                                                                                                  | Timer rate                                                                                                                                                                  | WDT reset rate                                                            | WDT INT rate                                                                |  |  |

| 2-0 | PS2:PS0 | $\begin{array}{cccccccc} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$ | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256                                                                                                 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 |  |  |

| 3   | PSC     | Prescaler assign<br>= 0, Timer0<br>= 1, WDT                                                                                                |                                                                                                                                                                             |                                                                           |                                                                             |  |  |

| 4   | TE      | = 0, Increment w                                                                                                                           | Timer0 source signal edge select bit:<br>= 0, Increment when low-to-high transition on RTCC pin for TIM0<br>= 1, Increment when high-to-low transition on RTCC pin for TIM0 |                                                                           |                                                                             |  |  |

| 5   | TS      | = 0, Internal instr                                                                                                                        | Timer0 source signal select bit:<br>= 0, Internal instruction clock cycle<br>= 1, Transition on RTCC pin                                                                    |                                                                           |                                                                             |  |  |

| 6   | INTF    | Interrupt enable flag (Read Only)<br>= 0, masked by DISI or hardware interrupt<br>= 1, enabled by ENI / RETIE instructions                 |                                                                                                                                                                             |                                                                           |                                                                             |  |  |

| 7   | INTEDG  | = 0, interrupt on                                                                                                                          | Interrupt edge select bit<br>= 0, interrupt on falling edge of INT pin<br>= 1, interrupt on rising edge of INT pin                                                          |                                                                           |                                                                             |  |  |

\* The first WDT Interrupt is 1/2 period after executing Reset function or CLRWDT instruction when the

Prescaler is assigned to Watch Dog Timer.

#

# 3.2 I/O Control Registers (Addressed by IOST, IOSTR instruction)

# • Control PortB I/O Mode Register: F6 (PortB)

The F6 register is both readable and writable.

- = 0, the relative I/O pin is in output mode.

- = 1, the relative I/O pin is in input mode.

# • PortB Input Change Interrupt Control Register: F9

The F9 register is both readable and writable.

| * Bit 0 ( PBEI0 ) : = 0, Disable the input change interrupt function of PB0 pin. |

|----------------------------------------------------------------------------------|

| = 1, Enable the input change interrupt function of PB0 pin.                      |

| * Bit 1 ( PBEI1 ): = 0, Disable the input change interrupt function of PB1 pin.  |

| = 1, Enable the input change interrupt function of PB1 pin.                      |

| * Bit 2 ( PBEI2 ): = 0, Disable the input change interrupt function of PB2 pin.  |

| = 1, Enable the input change interrupt function of PB2 pin.                      |

| * Bit 3 ( PBEI3 ): = 0, Disable the input change interrupt function of PB3 pin.  |

| = 1, Enable the input change interrupt function of PB3 pin.                      |

| * Bit 4 ( PBEI4 ): = 0, Disable the input change interrupt function of PB4 pin.  |

| = 1, Enable the input change interrupt function of PB4 pin.                      |

| * Bit 5 ( PBEI5 ) : = 0, Disable the input change interrupt function of PB5 pin. |

| = 1, Enable the input change interrupt function of PB5 pin.                      |

| * Bit 6 ( PBEI6 ): = 0, Disable the input change interrupt function of PB6 pin.  |

| = 1, Enable the input change interrupt function of PB6 pin.                      |

| * Bit 7 ( PBEI7 ): = 0, Disable the input change interrupt function of PB7 pin.  |

| = 1, Enable the input change interrupt function of PB7 pin.                      |

# • Prescaler of Timer0 and WDT Counter Register: FA

The FA register is readable.

The content of FA is the value of Prescaler Counter.

# • Pull Down Control Register: FB

The FB register is both readable and writable.

- \* Bit 0 ( /PDB4 ) : = 0, Enable the internal pull-down of PB4 pin.

- =1, Disable the internal pull-down of PB4 pin.

- \* Bit 1 ( /PDB5 ) : = 0, Enable the internal pull-down of PB5 pin.

- =1, Disable the internal pull-down of PB5 pin.

- \* Bit 2 ( /PDB6 ) : = 0, Enable the internal pull-down of PB6 pin.

- =1, Disable the internal pull-down of PB6 pin.

\* Bit 3 ( /PDB7 ) := 0, Enable the internal pull-down of PB7 pin.

=1, Disable the internal pull-down of PB7 pin.

\* Bit 4 ( /PDB0 ) := 0, Enable the internal pull-down of PB0 pin.

=1, Disable the internal pull-down of PB0 pin.

\* Bit 5 ( /PDB1 ) := 0, Enable the internal pull-down of PB1 pin.

=1, Disable the internal pull-down of PB1 pin.

\* Bit 6 ( /PDB2 ) := 0, Enable the internal pull-down of PB2 pin.

\* Bit 7 ( /PDB3 ) := 0, Enable the internal pull-down of PB3 pin.

=1, Disable the internal pull-down of PB3 pin.

# • Open Drain Control Register: FC

The FC register is both readable and writable.

- \* Bit 0 ( ODB0 ) : = 0, Disable the internal open-drain of PB0 pin.

- = 1, Enable the internal open-drain of PB0 pin.

- \* Bit 1 (ODB1): = 0, Disable the internal open-drain of PB1 pin.

= 1, Enable the internal open-drain of PB1 pin.

\* Bit 2 ( ODB2 ) : = 0, Disable the internal open-drain of PB2 pin. = 1, Enable the internal open-drain of PB2 pin.

\* Bit 3: General register read / write bit

- \* Bit 4 ( ODB4 ) : = 0, Disable the internal open-drain of PB4 pin.

- = 1, Enable the internal open-drain of PB4 pin.

- \* Bit 5 ( ODB5 ) : = 0, Disable the internal open-drain of PB5 pin.

= 1, Enable the internal open-drain of PB5 pin.

\* Bit 6 ( ODB6 ) : = 0, Disable the internal open-drain of PB6 pin.

= 1, Enable the internal open-drain of PB6 pin.

\* Bit 7 ( ODB7 ): = 0, Disable the internal open-drain of PB7 pin. = 1, Enable the internal open-drain of PB7 pin.

# Pull High Control Register: FD

The FD register is both readable and writable.

\* Bit 0 ( /PHB0 ) : = 0, Enable the internal pull-high of PB0 pin.

- = 1, Disable the internal pull-high of PB0 pin.

- \* Bit 1 ( /PHB1 ) : = 0, Enable the internal pull-high of PB1 pin.

- = 1, Disable the internal pull-high of PB1 pin.

- \* Bit 2 ( /PHB2 ) : = 0, Enable the internal pull-high of PB2 pin.

- = 1, Disable the internal pull-high of PB2 pin.

- \* Bit 3: General register read / write bit

\* Bit 4 ( /PHB4 ) : = 0, Enable the internal pull-high of PB4 pin.

- = 1, Disable the internal pull-high of PB4 pin.

- \* Bit 5 ( /PHB5 ) : = 0, Enable the internal pull-high of PB5 pin.

- = 1, Disable the internal pull-high of PB5 pin.

- \* Bit 6 ( /PHB6 ) : = 0, Enable the internal pull-high of PB6 pin.

- = 1, Disable the internal pull-high of PB6 pin.

\* Bit 7 ( /PHB7 ) : = 0, Enable the internal pull-high of PB7 pin.

= 1, Disable the internal pull-high of PB7 pin

# • System Control Register: FE

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WDTE  | EIS   | LVRE  |       | LPRE  | CONC  |       |       |

The FE register is both readable and writable.

\* Bit 0 ~ 1 : Not used.

\* Bit 2 (CONC) = 1, Enable Constant Sink Current Mode of PB1/IR pin.

PB1/IR Pin will provide constant output-low-sink current about 40mA when PB1/IR pin is configured as output mode.

= 0, Disable Constant Sink Current Mode of PB1/IR pin.

- \* Bit 3 (LPRE) = 1, Enable Low Power reset

- = 0, Disable Low Power reset

- \* Bit 4 : Not used.

- \* Bit 5 (LVRE) = 1, Enable low voltage reset.(Precise Low voltage reset selection by configuration word)

- = 0, Disable low voltage reset.(Precise Low voltage reset selection by configuration word)

- \* Bit 6 (EIS) = 1, External interrupt pin is selected. The I/O control bit of PB0 (bit 0 of F6) must be set to "1",

the status of INT pin can be read by reading PortB.

- = 0, PB0 is bi-directional I/O pin.

- \* Bit 7 (WDTE) = 1, Enable Watchdog timer.

= 0, Disable Watchdog timer.

## Interrupt Mask Register: FF

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | WDTIE |       |       |       | EXIE  | PBIE  | T0IE  |

The FF register is both readable and writable.

\* Bit 0 (T0IE) : = 1, Enable the Timer0 overflow interrupt.

= 0, Disable the Timer0 overflow interrupt.

\* Bit 1 (PBIE) : = 1, Enable the PortB input change interrupt.

= 0, Disable the PortB input change interrupt.

\* Bit 2 (EXIE) : = 1, Enable the External INT pin interrupt.

= 0, Disable the External INT pin interrupt.

- \* Bit 3 ~ 5 : Not used.

- \* Bit 6 (WDTIE) : If the watchdog interrupt function is enabled by programming configuration word,

- = 1, Enable watchdog interrupt.

- = 0, Disable watchdog interrupt.

\* Bit 7: Not used.

# 3.3 Special Function Registers (Addressed by SFUN, SFUNR instruction)

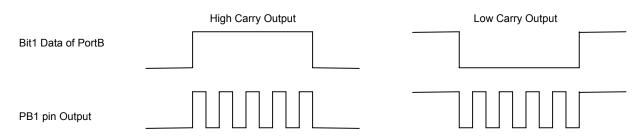

# • IR Control register: S6

| Bit 7                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2        | Bit 1     | Bit 0       |

|----------------------|-------|-------|-------|-------|--------------|-----------|-------------|

| IR Clock(Fosc) Input |       |       |       |       | 0:High Carry | IR Output | IR function |

| Frequency Selection  |       |       |       |       | output       | Frequency | 0:disable   |

| 0: 455KHz            |       |       |       |       | 1:Low Carry  | Secection | 1:enable    |

| 1: 3.58MHz           |       |       |       |       | output       | 0: 38K Hz |             |

|                      |       |       |       |       |              | 1: 57K Hz |             |

- \* The S6 register is only writable.

- \* If Bit0 is set "1" to enable IR function, the IR/PB1 pin will be auto configured to output mode and output the data of PortB bit1 in IR function mode.

- \* The "High Carry Output " means to output high data with IR carry to IR/PB1pin and the "Low Carry Output " is the opposite.

# FIGURE 3.3: Timing Chart of IR Carry Output

• Table High-Order Byte Pointer register (TBHP): S7

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       |       |       |       | D1    | D0    |

\* The S7 register is both readable and writable.

\* The content of TBHP will associate with ACC to be loaded into PC bits< 9:0 > when program executes CALLA or GOTOA instruction. Additionally, the TBHP register is used for high part address to access ROM code data in executing the TABLE instruction.

# • Table High-Order Byte Data register (TBH): S8

| ſ | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   |       |       | D5    | D4    | D3    | D2    | D1    | D0    |

\* The S8 register is only readable.

\* Move the high byte of the addressed ROM code to TBH register by TABLE instruction.

# 3.4 RESET

This device may be reset in one of the following events:

- (1) Power-on Reset: At power-up, this device will be kept in a reset condition until the power voltage on Reset pin has reached a logic high level.

- (2) Reset pin is "LOW" state input. (if Reset pin is configured as reset function.)

- (3) WDT time-out reset. (if WDT is enabled and WDT reset function is enabled.)

- (4) Low voltage reset. (if Low voltage function is enabled)

The contents of registers after reset are listed below:

| Address | Register                                           | Power-On Reset | Reset or WDT Reset |

|---------|----------------------------------------------------|----------------|--------------------|

| 00h     | INAR                                               | XXXX XXXX      | นนนน นนนน          |

| 01h     | Timer0                                             | XXXX XXXX      | นนนน นนนน          |

| 02h     | PCL                                                | 0000 0000      | 0000 0000          |

| 03h     | STATUS                                             | 0001 1xxx      | #00# #uuu          |

| 04h     | FSR                                                | 11xx xxxx      | 11uu uuuu          |

| 06h     | PortB                                              | XXXX XXXX      | นนนน นนนน          |

| 0Fh     | Interrupt Status Register                          | -0000          | -0000              |

| 10h-3Fh | General Storage Register                           | XXXX XXXX      | นนนน นนนน          |

| N/A     | ACC                                                | XXXX XXXX      | นนนน นนนน          |

| N/A     | TOMODE                                             | 0011 1111      | 0011 1111          |

| N/A     | Control PortB I/O Reg (F6)                         | 1111 1111      | 1111 1111          |

| N/A     | PortB Input Change Interrupt Control Register (F9) | 1111 1111      | 1111 1111          |

| N/A     | Prescaler of Timer0 and WDT Register(FA)           | 1111 1111      | 1111 1111          |

| N/A     | Pull Down Control Register (FB)                    | 1111 1111      | 1111 1111          |

| N/A     | Open Drain Control Register (FC)                   | 0000 0000      | 0000 0000          |

| N/A     | Pull High Control Register (FD)                    | 1111 1111      | 1111 1111          |

| N/A     | System Control Register(FE)                        | 101- 00        | 101- 00            |

| N/A     | Interrupt Mask Register (FF)                       | -0000          | -0000              |

| N/A     | IR Control register(S6)                            | 0000           | 0000               |

| N/A     | Table High-Order Byte Pointer register (S7)        | XX             | uu                 |

| N/A     | Table High-Order Byte Data register (S8):          | xx xxxx        | นน นนนน            |

Note: x = unknown, u = unchanged, - = unimplemented, # = see the following table

# TO/PD status after Reset:

| Condition                                                  | Status: bit 7<br>RST | Status: bit 4<br>TO | Status: bit 3<br>PD |

|------------------------------------------------------------|----------------------|---------------------|---------------------|

| Power-on Reset                                             | 0                    | 1                   | 1                   |

| Reset pin Reset (Non-SLEEP)                                | 0                    | u                   | u                   |

| Reset pin Wake-up Reset or Interrupt<br>Wake-up from SLEEP | 0                    | 1                   | 0                   |

| WDT Reset (Non-SLEEP)                                      | 0                    | 0                   | 1                   |

| WDT Wake-up Reset from SLEEP                               | 0                    | 0                   | 0                   |

| PortB Input Change Interrupt Wake-up<br>from SLEEP         | 1                    | 1                   | 0                   |

Note: u = unchanged

TO/PD status is affected by events:

| Event                                  | Status: bit 4<br>TO | Status: bit 3<br>PD |

|----------------------------------------|---------------------|---------------------|

| Power-on                               | 1                   | 1                   |

| SLEEP instruction                      | 1                   | 0                   |

| CLRWDT instruction                     | 1                   | 1                   |

| WDT Time-out when WDT reset is enabled | 0                   | u                   |

Note: u = unchanged

WDT wake-up from sleep mode: executing the SLEEP instruction can force this device entering into sleep mode (power saving mode). While system is in sleep mode, the WDT is cleared but keeps running. This device can be awakened by WDT time-out when WDT reset function is enabled or reset input on Reset pin.

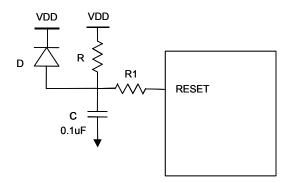

The following figure is power-on reset circuit for slow VDD power-up:

- It is recommended the R value should be not greater than 40k ohms to make sure the voltage of RSET pin can meet specification.

- The R1 value = 100 ohms ~ 1K ohms will prevent high current, ESD or Electrical Overstress flowing into RESET pin.

- The diode helps discharge quickly when power down.

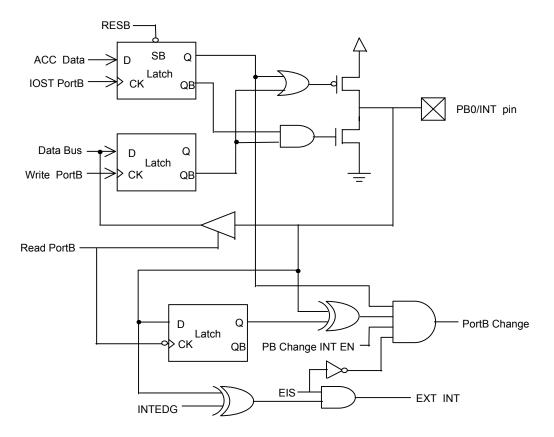

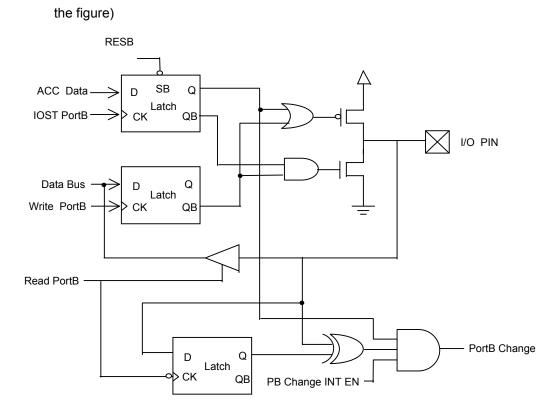

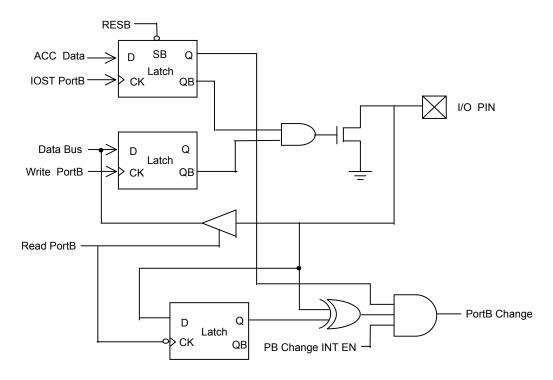

# 3.5 I/O Ports

The Port B are Bi-directional tri-state I/O ports. Port B is 8-pins I/O port. The Pin function of PB3/Reset will be decided by Bit13 of the Configuration Word. If this bit is set "1", the PB3/Reset Pin will be assigned to Reset function (Default) and forced as input; If this bit is cleared to "0", the PB3/Reset Pin will be assigned to digital I/O function.

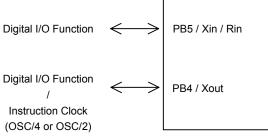

The Bit[2:0] of the Configuration Word can select oscillator mode. Besides, these bits can decide the pin function of PB5 and PB4.

The I/O Mode Register F6(Port B) can configure these I/O pins as output or input. The Pull Down Control Register FB can enable corresponding internal pull-down of PB3 ~ PB0, PB7 ~ PB4. The Open Drain Control Register FC can enable open drain function of PB7 ~ PB4 and PB2 ~ PB0. The Pull High Control Register FD can enable internal pull-high of PB7 ~ PB4 and PB2 ~ PB0.

Setting PortB Input Change Interrupt Control Register F9 can enable input Status Change Interrupt/Wake-up function.

PB0 also provide an external interrupt function by setting the EIS bit of the System Control Register FE. If the external interrupt function is enabled, the PB0 Input change interrupt function will be disabled automatically.

FIGURE 3.4: PB0/INT Equivalent Circuit (Pull-down, pull-high and open-drain are not shown in the figure)

FIGURE 3.5: PB1, PB2, PB4~PB7 Equivalent Circuit (Pull-down, pull-high and open-drain are not shown in

# FIGURE 3.5: PB3 Equivalent Circuit (Pull-down, pull-high and open-drain are not shown in the figure)

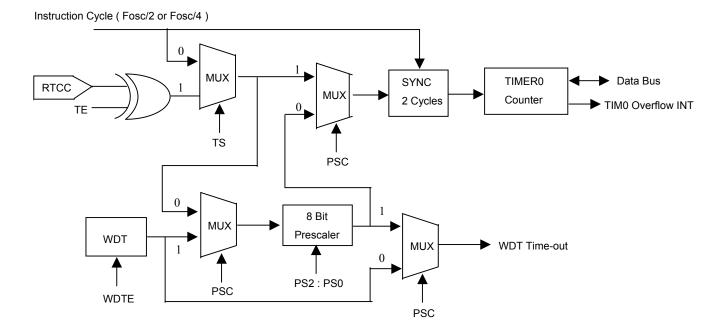

# 3.6 Real Time Clock (TIMER0) And Watchdog Timer

# 3.6.1 Timer0

Timer0 is an 8-bit timer/counter. The clock source of Timer0 can be from the internal clock or by an external clock source presented at the RTCC pin.

To select the internal clock source, bit 5 of the T0MODE register should be reset. In this mode, Timer0 will increase by 1 in every instruction cycle (without prescaler).

To select the external clock source, bit 5 of the T0MODE register should be set. In this mode, Timer0 will increase by 1 on every falling or rising edge of RTCC pin, which is controlled by bit 4 of T0MODE register.

# 3.6.2 Watchdog Timer(WDT)

The Watchdog Timer is a free running on-chip RC oscillator. This RC oscillator is separated from the RC oscillator of the OSCI pin. That means the WDT will keep running even when the oscillator driver is turned off, such as in sleep mode. During normal operation or in sleep mode, a WDT time-out will cause the device reset and the TO bit (bit 4 of STATUS register) will be cleared.

Without prescaler, the WDT time-out period is 18ms. This period can be increased by using the prescaler. The division ratio of prescaler is up to 1:128. Thus, the longest time-out period is approximately 2.3s.

# 3.6.3 Prescaler

The 8-bit prescaler may be assigned to either the Timer0 or the WDT through the PSC bit (bit 3 of the T0MODE register). Setting this bit assigns the prescaler to the WDT. Resetting this bit assigns the prescaler to the Timer0. The PS2:PS0 bits determine the prescale ratio. When assigned to Timer0, the prescaler will be cleared by instructions which write to Timer0 Register. A CLRWDT instruction will clear the WDT and prescaler when assigned to WDT. The prescaler can not be assigned to both the Timer0 and WDT simultaneously.

# 3.6.4 Switching Prescaler Assignment

The prescaler switch can be assigned by software control. To avoid an unintended RESET, the following program rule must be observed when changing the prescaler assignment from Timer0 to WDT :

CLRWDT MOVIA b'xxxx1xxx' CLRR TIM0 T0MODE

A CLRWDT instruction should be executed before changing the prescaler assignment from WDT to Timer0 :

CLRWDT MOVIA b'xxxx0xxx' T0MODE

# FIGURE 3.7: Block Diagram of Timer0 and WDT

# 3.7 Oscillator Configuration

This device supports six oscillator modes. The user can program the three Bit[2:0] of configuration word to select appropriate mode. These oscillator modes offered as:

- IRC: Internal Resistor and Capacitor oscillator

- EXT-R: External Resistor and internal Capacitor oscillator

- LF-XTAL: Low frequency crystal oscillator

- XTAL: Standard crystal oscillator

- HF-XTAL: High frequency crystal oscillator

- ERC: External Resistor and Capacitor oscillator

# 3.7.1 IRC Mode

The Internal Resistor and Capacitor mode (IRC) can be enabled by setting Bit[2:0] of configuration word and program Bit[5:3] to select output frequency of internal oscillator.

In IRC mode, PB5/Xin/Rin pin will be assigned to PB5 digital I/O, PB4/Xout pin will be assign to PB4 digital I/O or output instruction clock depend on the selection of configuration word Bit[2:0].

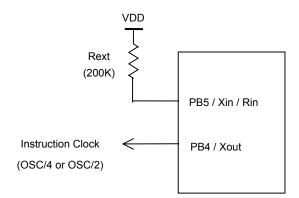

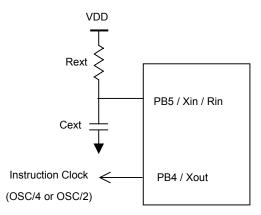

# 3.7.2 EXT-R Mode

In EXT-R mode adopts External resistor and internal capacitor to creat oscillator so PB5/Xin/Rin pin need to connect to Rext.By setting Bit[2:0] and Bit[5:3] of configuration word to enter EXT-R mode and select oscillator frequency. Resistance value of Rext can be tuned to produce more precise oscillator's frequency. The recommended value of Rext is 200K.

In EXT-R mode, PB4/Xout pin will output instruction clock.

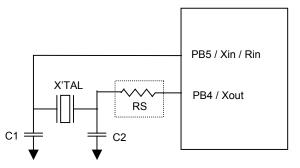

# 3.7.3 LF-XTAL, XTAL, HF-XTAL Mode

AM8EB series provide LF-XTAL, XTAL and HF-XTAL for different frequency crystal or ceramic oscillator. In these mode, a crystal or ceramic resonator is connected to Xin pin and Xout pin to create oscillation, refer to the specification of crystal or ceramic resonator to adopt appropriate C1, C2 or RS value.

| Mode    | Freq.      | C1(pF)   | C2(pF)   |

|---------|------------|----------|----------|

|         | 20 MHz     | 5 ~ 10   | 5 ~ 10   |

| HF-XTAL | 16 MHz     | 5 ~ 10   | 5 ~ 10   |

|         | 10 MHz     | 5 ~ 20   | 5 ~ 20   |

|         | 8 MHz      | 5 ~ 20   | 5 ~ 20   |

| XTAL    | 4 MHz      | 5 ~ 30   | 5 ~ 30   |

| ATAL    | 1 MHz      | 5 ~ 30   | 5 ~ 30   |

|         | 455 KHz    | 10 ~ 100 | 10 ~ 100 |

| LF-XTAL | 100 KHz    | 5 ~ 20   | 5 ~ 20   |

|         | 32.768 KHz | 5 ~ 30   | 5 ~ 30   |

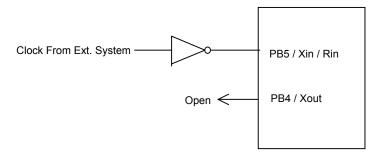

In LF-XTAL, XTAL or HF-XTAL mode, the Xin pin can be driven directly by an external clock source.

# 3.7.4 ERC Mode

The oscillator frequency of External Resistor and Capacitor Oscillator mode (ERC) will be influenced by the value of Rext, Cext, the supply voltage and the working temperature. In addition to these, the frequency will slightly vary between different chip due to the variation of manufacturing process parameter.

In order to keep stable oscillator frequency, the value of Rext should be less than 1M ohm, the value of Cext should be greater than 20pF. In ERC mode, PB4/Xout pin will output instruction clock.

# TABLE 3.3: ERC Oscillator Frequency Table

| Cext   | Rext | OSC @ 3V  | OSC @ 5V |

|--------|------|-----------|----------|

|        | 3.3K | 4.07 MHz  | 4.49 MHz |

| 20 pF  | 5.1K | 3.08 MHz  | 3.19 MHz |

| 20 pr  | 10K  | 1.82 MHz  | 1.76 KHz |

|        | 100K | 227 KHz   | 201 KHz  |

|        | 3.3K | 1.84 MH z | 1.8 MHz  |

| 100 pF | 5.1K | 1.29 MHz  | 1.22 MHz |

|        | 10K  | 703 KHz   | 640 KHz  |

|        | 100K | 79 KHz    | 69 KHz   |

|        | 3.3K | 915 KHz   | 848 KHz  |

| 200 pE | 5.1K | 622 KHz   | 567 KHz  |

| 300 pF | 10K  | 328 KHz   | 293 KHz  |

|        | 100K | 35 KHz    | 30.7 KHz |

# 3.8 Interrupts

The AM8EB051A has four sources of interrupt:

- Timer0 overflow

- PB input change

- External Interrupt Pin

- Watchdog time out Interrupt (If the function is enabled by setting the configuration word.)

Interrupt Status Register(R0F) is the interrupt flag register that recodes the interrupt requests in the relative flags. The global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction. Individual interrupts can be enabled/disabled through their corresponding enable bits in Interrupt Mask Register.

When one of the interrupt occurs, the next instruction will be fetched from address 008H. Once in the interrupt service routine, the source of an interrupt can be determined by polling Interrupt Status Register(R0F). The interrupt flag bit must be cleared by program before leaving the interrupt service routine and before interrupts are enabled to avoid recursive interrupts. The RETFIE instruction exits the interrupt routine and enables the global interrupt.

The flag bit (except PBIF bit) in Interrupt Status Register is set by interrupt event regardless of the status of its mask bit or the execution of ENI. Reading the Interrupt Status Register will be the logic AND of the Interrupt Status Register and Interrupt Mask Register.

When an interrupt is generated by the INT instruction, the next instruction will be fetched from address 001h.

# 3.8.1 External INT Interrupt

External interrupt on INT pin is rising or falling edge triggered can be selected by INTEDG bit of T0MODE Register. When a valid edge appears on the INT pin, then the flag bit EXIF of the Interrupt Status Register is set. Clearing the EXIE bit of Interrupt Mask Register can disable this interrupt.

# 3.8.2 Timer0 Interrupt

An overflow (FFh  $\rightarrow$  00h) in the Timer0 register will set the flag bit T0IF. Clearing T0IE bit of the Interrupt Mask Register can disable this interrupt.

# 3.8.3 Port B Input Change Interrupt

An input change on PB<7:0> will set the flag bit PBIF. Clearing PBIE bit of the Interrupt Mask Register can disable this interrupt.

Setting the PortB Input Change Interrupt Control Register (F9) can enable the PortB Input Change Interrupt individually. Reading PortB is necessary before the port B input change interrupt is enabled. When the pin is configured as output or PB0 pin is assigned as INT pin, the Input Change Interrupt

function will be disabled. Additionally, the PB5/Xin/Rin pin, PB4/Xout pin and RB3/Reset pin must be on digital I/O mode for PortB Input Change interrupt function.

# 3.8.4 Watchdog timer out Interrupt

Programming configuration word can enable the watchdog interrupt function. If this function is enabled, a WDT time-out will set the flag bit WDTIF. Clearing WDTIE bit of the Interrupt Mask Register can disable this interrupt.

# 3.9 Power-Down Mode (Sleep)

Executing a SLEEP instruction enters power-down mode. When SLEEP instruction is executed, the PD bit of Status register will be cleared, the TO bit will be set, the Watchdog Timer will be cleared and keeps running, and the oscillator driver is turned off. All I/O pins maintain the status they had before the SLEEP instruction was executed.

# 3.9.1 Wake-up from SLEEP Mode

The device can wake-up from SLEEP mode through one of the following events.

- 1. External reset input on Reset pin.

- 2. WDT time-out reset or WDT time-out interrupt (depends on which one is enabled by setting configuration word).

- 3. Interrupt from RB0/INT pin, or PortB change interrupt. (if enabled)

External reset input on Reset pin and WDT time-out reset will cause a device reset. The PD and TO bits can be used to determine the cause of device reset. The PD bit is set on power-up and is cleared when SLEEP instruction is executed. The TO bit is cleared if a WDT reset occurred.

An interrupt event is intended to wake-up the device, the corresponding interrupt function should be enabled before SLEEP. If ENI is executed before SLEEP, the program will branch to the interrupt address (008h) after wake-up. If DISI is executed before SLEEP, the device will continue execution at the instruction next to SLEEP instruction after wake-up.

# 3.10 Configuration Word

| Bit     | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,1,0   | Fosc<2:0>    | <ul> <li>=000, <u>EXT-R</u> mode (External resistor and internal capacitor), PB5/Xin/Rin pin will connect to Rext and PB4/Xout pin will output instruction clock.</li> <li>=001, <u>IRC</u> mode (Internal RC), PB5/Xin/Rin pin will be assigned to PB5 and <i>PB4/Xout pin will output instruction clock</i>.</li> <li>=011, <u>IRC</u> mode (Internal RC), PB5/Xin/Rin pin will be assigned to PB5 and <i>PB4/Xout pin will be assigned to PB4</i>.</li> <li>=100, <u>LF-XTAL</u> mode.</li> <li>=110, <u>HF-XTAL</u> mode.</li> <li>=111, <u>ERC</u> mode (External RC), PB4/Xout pin will output instruction clock.</li> </ul> |

| 5,4,3   | IEF<2:0>     | IRC / EXT-R frequency selection<br>=000, IRC= 20MHz<br>=001, IRC= 16MHz<br>=010, IRC= 8MHz<br>=011, IRC= 4MHz<br>=100, IRC= 2MHz<br>=101, IRC= 1MHz<br>=110, IRC = 455KHz<br>=111, IRC = 32KHz (Default)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6       | WDTEN        | =1, Watchdog Timer enable <i>(Default)</i><br>=0, Watchdog Timer disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7       | WDTREN       | =1, Watchdog Timer reset enable <i>(Default)</i><br>=0, Watchdog Timer interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8       | CLK          | Instruction period selection<br>=1, four oscillator periods <i>(Default)</i><br>=0, two oscillator periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11,10,9 | LVR<2:0>     | Precise Low voltage reset selection<br>=001, enable, LVR voltage = 2.0V<br>=010, enable, LVR voltage = 2.6V<br>=011, enable, LVR voltage = 2.8V<br>=100, enable, LVR voltage = 3.2V<br>=101, enable, LVR voltage = 3.6V<br>=110, enable, LVR voltage = 4.3V<br>=111, disable ( <i>Default</i> )                                                                                                                                                                                                                                                                                                                                    |

| 12      | PB3ENB       | Pin Function Selection of PB3/Reset<br>=1, assigned to Reset function and force PB3/Reset to input Pin <i>(Default)</i><br>=0, assigned to PB3 digital I/O function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13      | Code-protect | =1, EPROM unprotected <i>(Default)</i><br>=0, EPROM protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# 4. Instruction Set

| AM8EB051A include total 55 instructions, | and summarized in the following table |

|------------------------------------------|---------------------------------------|

|                                          |                                       |

| Mnemonic<br>Operands | Description                                | Cycles          | Instruction<br>Code | Status<br>Affected |

|----------------------|--------------------------------------------|-----------------|---------------------|--------------------|

| NOP                  | No operation                               | 1               | 00 0000 0000 0000   | -                  |

| SLEEP                | Go into standby mode                       | 1               | 00 0000 0000 0001   | TO, PD             |

| CLRWDT               | Clear Watchdog Timer                       | 1               | 00 0000 0000 0010   | TO, PD             |

| T0MODE               | Load T0MODE Register                       | 1               | 00 0000 0000 0011   | -                  |

| ENI                  | Enable Interrupt                           | 1               | 00 0000 0000 0100   |                    |

| IOST F               | Load IOST Register                         | 1               | 00 0000 0000 ffff   | -                  |

| RET                  | Return from subroutine                     | 2               | 00 0000 0001 0000   | -                  |

| RETIE                | Return from interrupt,<br>Enable Interrupt | 2               | 00 0000 0001 0001   | -                  |

| DAA                  | Decimal Adjust ACC                         | 1               | 00 0000 0001 0010   | С                  |

| DISI                 | Disable Interrupt                          | 1               | 00 0000 0001 0011   | -                  |

| T0MODER              | Move T0MODE Register to ACC                | 1               | 00 0000 0001 0100   | -                  |

| IOSTR F              | Move IOST Register to ACC                  | 1               | 00 0000 0001 ffff   | -                  |

| SFUN S               | Load SFUN Register                         | 1               | 00 0000 0010 ssss   | -                  |

| SFUNR S              | Move SFUN Register to ACC                  | 1               | 00 0000 0011 ssss   | -                  |

| MOVAR R              | Move ACC to R                              | 1               | 00 0000 1rrr rrrr   | -                  |

| MOVR R, d            | Move R                                     | 1               | 00 0001 drrr rrrr   | Z                  |

| CLRA                 | Clear ACC                                  | 1               | 00 0010 0000 0000   | Z                  |

| INT                  | S/W interrupt                              | 3               | 00 0010 0001 0000   | -                  |

| TABLEA               | Read ROM Code to TBH and ACC               | 2               | 00 0010 0001 0001   | -                  |

| CALLA                | Call subroutine                            | 2               | 00 0010 0001 0010   | -                  |

| GOTOA                | Unconditional branch                       | 2               | 00 0010 0001 0011   | -                  |

| CLRR R               | Clear R                                    | 1               | 00 0010 1rrr rrrr   | Z                  |

| ADDAR R, d           | Add ACC and R                              | 1               | 00 0011 drrr rrrr   | C, DC, Z           |

| SUBAR R, d           | Subtract ACC from R                        | 1               | 00 0100 drrr rrrr   | C, DC, Z           |

| INCR R, d            | Increment R                                | 1               | 00 0101 drrr rrrr   | Z                  |

| DECR R, d            | Decrement R                                | 1               | 00 0110 drrr rrrr   | Z                  |

| COMR R, d            | Complement R                               | 1               | 00 0111 drrr rrrr   | Z                  |

| ANDAR R, d           | AND ACC with R                             | 1               | 00 1000 drrr rrrr   | Z                  |

| IORAR R, d           | Inclusive OR ACC with R                    | 1               | 00 1001 drrr rrrr   | Z                  |

| XORAR R, d           | Exclusive OR ACC with R                    | 1               | 00 1010 drrr rrrr   | Z                  |

| RRR R, d             | Rotate right R                             | 1               | 00 1011 drrr rrrr   | С                  |

| RLR R, d             | Rotate left R                              | 1               | 00 1100 drrr rrrr   | С                  |

| SWAPR R, d           | Swap halves R                              | 1               | 00 1101 drrr rrrr   | -                  |

| INCRSZ R, d          | Increment R, Skip if 0                     | 1 or<br>2(skip) | 00 1110 drrr rrrr   | -                  |

| DECRSZ R, d          | Decrement R, Skip if 0                     | 1 or<br>2(skip) | 00 1111 drrr rrrr   | -                  |

| RETIA I              | Return, place immediate in A               | 2               | 01 0000 iiii iiii   | -                  |

| MOVIA I              | Move immediate to ACC                      | 1               | 01 0001 iiii iiii   | -                  |

| ANDIA I              | AND immediate with ACC                     | 1               | 01 0010 iiii iiii   | Z                  |

| IORIA I              | Inclusive OR immediate with ACC            | 1               | 01 0011 iiii iiii   | Z                  |

| XORIA I              | Exclusive OR immediate with ACC            | 1               | 01 0100 iiii iiii   | Z                  |

| ADDIA I              | Add ACC and immediate                      | 1               | 01 0101 iiii iiii   | C, DC, Z           |

| ADCIA I              | Add ACC and immediate with Carry           | 1               | 01 0110 iiii iiii   | C, DC, Z           |

| SUBIA I              | Subtract ACC from immediate                | 1               | 01 0111 iiii iiii   | C, DC, Z           |

|                      | 2'                                         |                 |                     | Rev 1.0 200        |

| Mnemonic<br>Operands | Description                           | Cycles          | Instruction<br>Code | Status<br>Affected |

|----------------------|---------------------------------------|-----------------|---------------------|--------------------|

| SBCIA I              | Subtract ACC and Carry from immediate | 1               | 01 1000 iiii iiii   | C, DC, Z           |

| CALL I               | Call subroutine                       | 2               | 01 1001 iiii iiii   | -                  |

| GOTO I               | Unconditional branch                  | 2               | 01 101i iiii iiii   | -                  |

| ADCAR R, d           | Add ACC and R with Carry              | 1               | 01 1100 drrr rrrr   | C, DC, Z           |

| SBCAR R, d           | Subtract ACC and Carry from R         | 1               | 01 1101 drrr rrrr   | C, DC, Z           |

| CMPAR R              | Compare R with ACC                    | 1               | 01 1110 1rrr rrrr   | C, Z               |

| BCR R, bit           | Clear bit in R                        | 1               | 10 11bb brrr rrrr   | -                  |

| BSR R, bit           | Set bit in R                          | 1               | 10 10bb brrr rrrr   | -                  |

| BTRSC R, bit         | Test bit in R and skip if clear       | 1 or<br>2(skip) | 10 01bb brrr rrrr   | -                  |

| BTRSS R, bit         | Test bit in R and skip if set         | 1 or<br>2(skip) | 10 00bb brrr rrrr   | -                  |

| LCALL I              | Call subroutine                       | 2               | 11 Oiii iiii iiii   | -                  |

| LGOTO I              | Unconditional branch                  | 2               | 11 liii iiii iiii   | -                  |

Legend:

# b : Bit position WDT : Watchdog Timer

i : Immediate data

PD : Power down flag

ACC : Accumulator TO : Time overflow bit

$\mathsf{R}:(\mathsf{r}_6\,\mathsf{r}_5\,\mathsf{r}_4\,\mathsf{r}_3\,\mathsf{r}_2\,\mathsf{r}_1\,\mathsf{r}_0)$

Z : Zero flag

l:(i7 i6 i5 i4 i3 i2 i1 i0)

S : (s<sub>3</sub> s<sub>2</sub> s<sub>1</sub> s<sub>0</sub>)

d 01 : Destination

If d is "0", the result is stored in the ACC register.

C : Carry flag

If d is "1", the result is stored back in register R.

# R : Register address

$\label{eq:toyoff} \begin{array}{l} \text{T0MODE}: \text{T0MODE} \ \text{register} \\ \text{IOST}: \text{I/O} \ \text{port control register} \\ \text{DC}: \text{Digital carry flag} \\ \text{F}: (f_3 \ f_2 \ f_1 \ f_0) \ {}_{5\text{-}f} \end{array}$

ADCAR (Add ACC and R with Carry) Syntax: ADCAR R, d Operands: 0≤ R≤ 127 d∈[0,1] Operation: ACC + R + C → dest Status Affected: C, DC, Z Description: Add the contents of the ACC register and register 'R' with Carry. If 'd' is 0, the result is stored in the ACC register. If 'd' is '1', the result is stored back in register 'R'. Cycles: 1

# ADCIA (Add ACC and Immediate with Carry)

Syntax: ADCIA I

Operands:  $0 \le I \le 255$

Operation: ACC + I + C  $\rightarrow$  ACC

Status Affected: C, DC, Z

Description: Add the contents of the ACC register and the 8-bit immediate 'l' with Carry. The result is placed in the ACC register.

Cycles: 1

# ADDAR (Add ACC and R)

Syntax: ADDAR R, d

Operands:  $0 \le R \le 127$

d∈[0,1]

Operation: ACC + R → dest

Status Affected: C, DC, Z

Description: Add the contents of the ACC register and register

'R'. If 'd' is 0, the result is stored in the ACC register. If 'd' is '1', the result is stored back in register 'R'.

Cycles: 1

# ADDIA (Add ACC and Immediate)

Syntax: ADDIA I

Operands:  $0 \le I \le 255$

Operation: ACC + I → ACC Status Affected: C, DC, Z Description: Add the contents of the ACC register with the 8-bit immediate 'I'. The result is placed in the ACC register. Cycles: 1

### ANDAR (AND ACC and R)

Syntax: ANDAR R, d Operands: 0≤ R≤ 127 d∈[0,1] Operation: ACC and R → dest Status Affected: Z Description: The contents of the ACC register are AND'ed with register 'R'. If 'd' is 0, the result is stored in the ACC register. If 'd' is '1', the result is stored back in register 'R'.

Cycles: 1

### ANDIA (AND Immediate with ACC)

Syntax: ANDIA I Operands: 0≤ I ≤ 255 Operation: ACC AND I → ACC Status Affected: Z Description: The contents of the ACC register are AND'ed with the 8-bit immediate 'I'. The result is placed in the ACC register.

Cycles: 1

## BCR (Clear Bit in R)

Syntax: BCR R, b Operands:  $0 \le R \le 127$   $0 \le b \le 7$ Operation:  $0 \rightarrow R < b >$ Status Affected: None Description: Clear bit 'b' in register 'R'. Cycles: 1

BSR (Set Bit in R) Syntax: BSR R, b Operands:  $0 \le R \le 127$   $0 \le b \le 7$ Operation: 1 → R <b> Status Affected: None Description: Set bit 'b' in register 'R'. Cycles: 1

# BTRSC (Test Bit in R, Skip if Clear)

Syntax: BTRSC R, b

Operands:  $0 \le R \le 127$

$0 \le b \le 7$

Operation: Skip if R<b> = 0

Status Affected: None

Description: If bit 'b' in register 'R' is 0, the next instruction is skipped. If bit 'b' is 0, the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead making this a 2-cycle instruction..

Cycles: 1(2)

# BTRSS (Test Bit in R, Skip if Set)

Syntax: BTRSS R, b

Operands:  $0 \le R \le 127$

$0 \leq b {\leq} 7$

Operation: Skip if R<b> = 1

Status Affected: None

Description: If bit 'b' in register 'R' is '1', the next instruction is skipped. If bit 'b' is '1', the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a 2-cycle instruction.

Cycles: 1(2)

### **CALL** (Call Subroutine)

Syntax: CALL I Operands:  $0 \le I \le 255$ Operation: PC +1  $\rightarrow$  Top of Stack; Status<5>  $\rightarrow$  PC<9> " 0 "  $\rightarrow$  PC<8> I  $\rightarrow$  PC<7:0> Status Affected: None Description: Subroutine call. First, return address (PC+1) is pushed onto the stack. The 8-bit immediate address is loaded into PC bits <7:0>. The Status <5> load into PC<9>, PC<8> is cleared. CALL is a two-cycle instruction.

Cycles: 2

### CALLA (Call Subroutine)

Syntax: CALLA Operands: None Operation: PC +1 → Top of Stack; {[ TBHP], [ACC ]}→ PC< 9:0 > Status Affected: None Description: Subroutine call. First, return address (PC+1) is pushed onto the stack. The content of TBHP and ACC is loaded into PC bits < 9:0 >. CALLA is a two-cycle instruction.

Cycles: 2

### **<u>CLRA</u>** (Clear ACC)

Syntax: CLRA Operands: None Operation:  $00h \rightarrow ACC;$   $1 \rightarrow Z$ Status Affected: Z Description: The ACC register is cleared. Zero bit (Z) is set. Cycles: 1

# AM8EB051A

CLRR (Clear R) Syntax: CLRR R Operands:  $0 \le R \le 127$ Operation:  $00h \rightarrow R$ ;  $1 \rightarrow Z$ Status Affected: Z Description: The contents of register 'R' are cleared and the Z bit is set. Cycles: 1

# **CLRWDT** (Clear Watchdog Timer)

Syntax: CLRWDT

Operands: None

Operation:  $00h \rightarrow WDT$ ;

$00h \rightarrow WDT$  prescaler (if assigned);

1 → TO;

1→ PD

Status Affected: TO,PD

Description: The CLRWDT instruction resets the WDT. It also resets the prescaler if the prescaler is assigned to the WDT and not Timer0. Status bits TO and PD are set.

Cycles: 1

# <u>COMR</u> (Complement R)

Syntax: COMR R, d Operands:  $0 \le R \le 127$

d∈[0,1]

Operation:  $\sim R \rightarrow dest$

Status Affected: Z

Description: The contents of register 'R' are complemented. If 'd' is 0, the result is stored in the ACC register. If 'd' is 1, the result is stored back in register 'R'.

Cycles: 1

CMPAR (Compare ACC and R) Syntax: CMPAR R Operands: 0≤ R≤ 127 Operation: R - ACC Status Affected: C, Z Description: Compare ACC and R. Subtract (2's complement method) the ACC register from register 'R' that will not change the content of ACC and R. Cycles: 1

DAA (Adjust ACC's data format from HEX to DEC)

Syntax: DAA Operands: None Operation: If [ACC<3:0> > 9] or [DC=1] then A<3:0> + 6  $\rightarrow$  ACC<3:0> ; If [ACC<7:4 > > 9] or [C=1] then A<7:4> + 6  $\rightarrow$  ACC<7:4> Status Affected: C Description: Convert the ACC data from hexadecimal to

decimal format after addition operation and restored to ACC.

DAA instruction must be placed at the next Instruction of addition operation.

Cycles: 1

DECR (Decrement R) Syntax: DECR R, d Operands:  $0 \le R \le 127$ d∈[0,1] Operation: R - 1 → dest Status Affected: Z Description: Decrement register 'R'. If 'd' is 0, the result is stored in the ACC register. If 'd' is 1, the result is stored back in register 'R'.

Cycles: 1

# AM8EB051A

DECRSZ (Decrement R, Skip if 0) Syntax: DECRSZ R, d Operands: 0≤ R≤ 127 d∈[0,1] Operation: R - 1 → dest; skip if result =0 Status Affected: None Description: The contents of register 'R' are decremented. If 'd' is 0, the result is placed in the ACC register. If 'd' is 1, the result is placed back in register 'R'. If the result is 0, the next instruction which is already fetched is discarded and a NOP is executed instead making it a two-cycle instruction. Cycles: 1(2)

### **DISI** (Disable Interrupt)

Syntax: DISI Operands: None Operation: 0 → INT; Status Affected: None Description: Disable global interrupt. Cycles: 1

# ENI (Enable Interrupt)

Syntax: ENI Operands: None Operation: 1 → INT; Status Affected: None Description: Enable global interrupt. Cycles: 1

# **GOTO** (Unconditional Branch)

Syntax: GOTO I Operands: 0≤ I ≤511 Operation: Status<5> → PC<9> I → PC<8:0> Status Affected: None Description: GOTO is an unconditional branch. The 9-bit immediate address is loaded into PC bits <8:0>. PC<9> is loaded from the Status <5>. GOTO is a two-cycle instruction.

Cycles: 2

### **GOTOA** (Unconditional Branch)

Syntax: GOTOA Operands: None Operation: {[ TBHP], [ACC ]}→ PC< 9:0 > Status Affected: None Description: GOTOA is an unconditional branch. The content of TBHP and ACC is loaded into PC bits < 9:0 >. GOTOA is a two-cycle instruction.

Cycles: 2

# INCR (Increment R)Syntax: INCR R, dOperands: $0 \le R \le 127$ $d \in [0,1]$ Operation: $R + 1 \rightarrow dest$ Status Affected: ZDescription: The contents of register 'R' are incremented. If 'd'is 0, the result is placed in the ACC register. If 'd'is 1, the result is placed back in register 'R'.

Cycles: 1

### **INCRSZ** (Increment R, Skip if 0)

Syntax: INCRSZ R, d Operands: 0≤ R≤ 127 d∈[0,1] Operation: R + 1 → dest, skip if result = 0 Status Affected: None Description: The contents of register 'R' are incremented. If 'd' is 0, the result is placed in the ACC register. If 'd' is 1, the result is placed back in register 'R'. If the

result is 0, the next instruction which is already

fetched is discarded and a NOP is executed instead making it a two-cycle instruction. Cycles: 1(2)

# INT (S/W Interrupt)

Syntax: INT Operands: None Operation: PC + 1  $\rightarrow$  Top of Stack, 001h  $\rightarrow$  PC

Status Affected: None

Description: Interrupt subroutine call. First, return address (PC+1) is pushed onto the stack. The address 001h is loaded into PC bits <9:0>.

Cycles: 3

# IORAR (OR ACC with R)

Syntax: IORAR R, d

Operands:  $0 \le R \le 127$

d∈[0,1]

Operation: ACC or  $R \rightarrow dest$

Status Affected: Z

Description: Inclusive OR the ACC register with register 'R'. If 'd' is 0 the result is placed in the ACC register. If 'd' is 1 the result is placed back in register 'R'. Cycles: 1

# IORIA (OR Immediate with ACC)

Syntax: IORIA I

Operands:  $0 \le I \le 255$

Operation: ACC or I  $\rightarrow$  ACC

Status Affected: Z

Description: The contents of the ACC register are OR'ed with the 8-bit immediate 'I'. The result is placed in the ACC register.

Cycles: 1

IOST (Load IOST Register) Syntax: IOST F Operands: F = 5,6, 7...f Operation: ACC → IOST register F Status Affected: None Description: IOST register 'F' (F= 5,6,7...f) is loaded with the contents of the ACC register.

Cycles: 1

# **IOSTR** (Move IOST Register to ACC)

Syntax: IOSTR F Operands: F = 5,6, 7...f Operation: IOST register F →ACC Status Affected: None Description: Move the contents of IOST register 'F' (F= 5,6,7...f) to ACC register.

Cycles: 1

# LCALL (Call Subroutine)

Syntax: LCALL I Operands: 0≤ I ≤2047 Operation: PC +1 → Top of Stack; I → PC<10:0> Status Affected: None Description: Subroutine call. First, return address (PC+1) is pushed onto the stack. The 11-bit immediate address is loaded into PC bits <10:0>. LCALL is a

two-cycle instruction.

Cycles: 2

# LGOTO (Unconditional Branch)

Syntax: LGOTO I Operands:  $0 \le I \le 2047$ Operation:  $I \rightarrow PC<10:0>$ Status Affected: None

Description: LGOTO is an unconditional branch. The 11-bit immediate value is loaded into PC bits <10:0>. LGOTO is a two-cycle instruction.

Cycles: 2

# MOVAR (Move ACC to R)

Syntax: MOVAR R Operands:  $0 \le R \le 127$ Operation: ACC  $\rightarrow R$ Status Affected: None Description: Move data from the ACC register to register 'R'. Cycles: 1

# MOVIA (Move Immediate to ACC)

Syntax: MOVIA I

Operands:  $0 \le I \le 255$

Operation: I → ACC

Status Affected: None

Description: The 8-bit immediate 'l' is loaded into the ACC register. The don't cares will assemble as 0s. Cycles: 1

# MOVR (Move R)

Syntax: MOVR R, d

Operands:  $0 \le R \le 127$

d∈[0,1]

Operation:  $R \rightarrow dest$

Status Affected: Z

Description: The contents of register 'R' is moved to destination 'd'. If 'd' is 0, destination is the ACC register. If 'd' is 1, the destination is file register 'R'. 'd' is 1 is useful to test a file register since status flag Z is affected.

Cycles: 1

# NOP (No Operation)

Syntax: NOP Operands: None Operation: No operation Status Affected: None Description: No operation. Cycles: 1

# **<u>RETIE</u>** (Return from Interrupt, Enable Interrupt)

Syntax: RETIE Operands: None Operation: Top of Stack → PC Status Affected: None Description: The program counter is loaded from the top of the stack (the return address) and enable Interrupt function. This is a two-cycle instruction.

Cycles: 2

# **<u>RETIA</u>** (Return with Immediate in ACC)

Syntax: RETIA I Operands: 0≤ I ≤ 255 Operation: I → ACC; Top of Stack → PC Status Affected: None Description: The ACC register is loaded with the 8-bit immediate 'I'. The program counter is loaded from the top of the stack (the return address). This is a

two-cycle instruction.

Cycles: 2

# RET (Return from Subroutine)

Syntax: RET Operands: None Operation: Top of Stack → PC Status Affected: None

Description: The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction.

Cycles: 2

# RLR (Rotate Left f through Carry)

Syntax: RLR R, d

Operands:  $0 \le R \le 127$

d∈[0,1]

Operation:  $R < 7 > \rightarrow C$ ;

$R<6:0> \rightarrow dest<7:1>;$

$C \rightarrow dest<0>$

Status Affected: C

Description: The contents of register 'R' are rotated one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the ACC register. If 'd' is 1, the result is stored back in register 'R'.

Cycles: 1

# RRR (Rotate Right f through Carry)

Syntax: RRR R, d Operands:  $0 \le R \le 127$  $d \in [0,1]$

Operation:  $C \rightarrow dest < 7>$ ;

$R<7:1> \rightarrow dest<6:0>;$

$R<0> \rightarrow C$

Status Affected: C

Description: The contents of register 'R' are rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in the ACC register. If 'd' is 1, the result is placed back in register 'R'.

Cycles: 1

# **SBCAR** (Subtract ACC and Carry from R)

Syntax: SUBAR R, d Operands:  $0 \le R \le 127$  $d \in [0,1]$  Operation: R - ACC - C → dest Status Affected: C, DC, Z Description: Subtract (2's complement method) the ACC and Carry register from register 'R'. If 'd' is 0, the result is stored in the ACC register. If 'd' is 1, the result is stored back in register 'R'.

Cycles: 1

# **<u>SBCIA</u>** (Subtract ACC and Carry from Immediate)

Syntax: SBCIA I Operands: 0≤ I ≤ 255 Operation: I - ACC - C→ ACC Status Affected: C, DC, Z Description: Subtract (2's complement method) the ACC register and Carry from the 8-bit immediate 'I'. The result is placed in the ACC register.

Cycles: 1

# SFUN (Load SFUN Register)

Syntax: SFUN S Operands: S = 0,1,2... Operation: ACC → SFUN register S Status Affected: None Description: SFUN register 'S' (S=0,1,2...) is loaded with the contents of the ACC register.

Cycles: 1

## SFUNR (Move SFUN Register to ACC)

Syntax: SFUNR S Operands: S = 0,1,2... Operation: SFUN register S →ACC Status Affected: None Description: Move the contents of SFUN register 'S' (S= 0,1,2...) to ACC register.

Cycles: 1

SLEEP (Enter SLEEP Mode)Syntax: SLEEPOperands: NoneOperation:  $00h \rightarrow WDT$ ; $00h \rightarrow WDT$  prescaler; $1 \rightarrow TO$ ; $0 \rightarrow PD$ Status Affected: TO,PDDescription: Time-out status bit (TO) is set. The power-down<br/>status bit (PD ) is cleared. The WDT and its<br/>prescaler are cleared. The processor is put into<br/>SLEEP mode.Cycles: 1

# SUBAR (Subtract ACC from R)

Syntax: SUBAR R, d

Operands:  $0 \le R \le 127$

d∈[0,1]

Operation: R - ACC  $\rightarrow$  dest

Status Affected: C, DC, Z

Description: Subtract (2's complement method) the ACC register from register 'R'. If 'd' is 0, the result is stored in the ACC register. If 'd' is 1, the result is stored back in register 'R'.

Cycles: 1

# **SUBIA** (Subtract ACC from Immediate)

Syntax: SUBIA I

Operands:  $0 \le I \le 255$

Operation: I - ACC  $\rightarrow$  ACC

Status Affected: C, DC, Z

Description: Subtract (2's complement method) the ACC register from the 8-bit immediate 'I'. The result is placed in the ACC register.

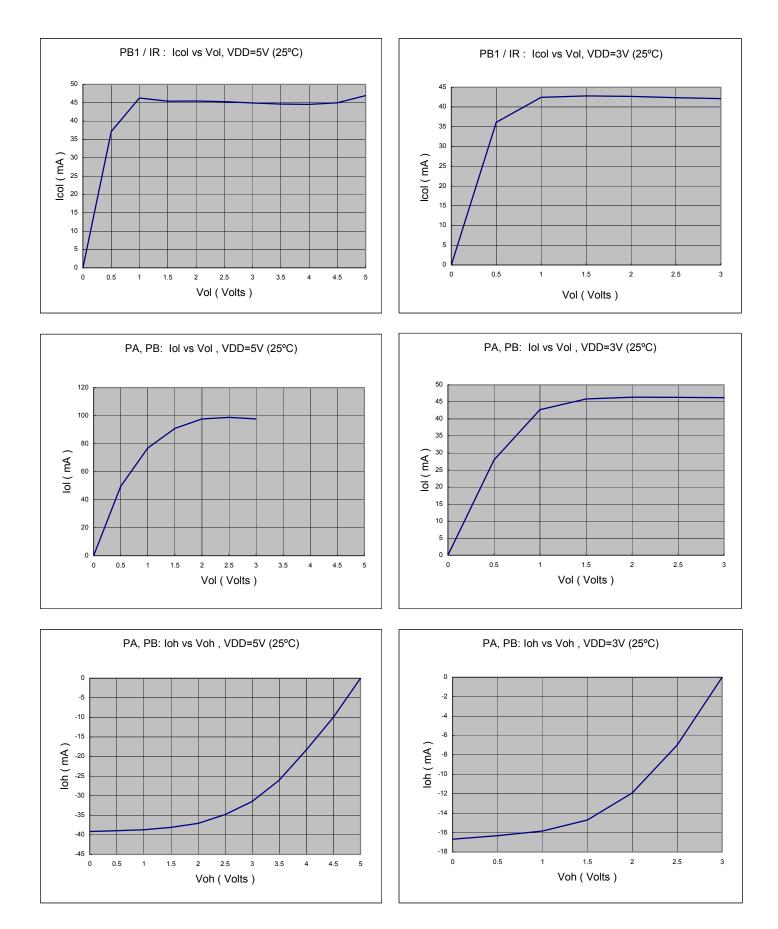

Cycles: 1