#### 1. Feature

ROM: 1K x 14 bits RAM: 25 x 8 bits STACK: 2 Levels

I/O ports: 12 I/O PAD Timer/counter: 8bits x1 (TMR0)

Prescaler: 8 Bits

Watchdog Timer: On chip WDT is based on internal RC oscillator. The shortest period is

20mS; user can extend the WDT overflow period to 2.6S by using

prescaler.

Power-On Reset

Reset Timer: 20 mS (5V)

Four external Oscillate modes: RC, LP Crystal, NT Crystal and HS Crystal.

Operation Voltage: 2.2V 5.5V

Instruction set: 79 Reset vector: 3FFH

# 2. Pin Definition & Pad Assignment

| PA <sub>2</sub> | 1 | 18 | PA <sub>1</sub>  |

|-----------------|---|----|------------------|

| PA <sub>3</sub> | 2 | 17 | $PA_0$           |

| RTCC            | 3 | 16 | OSC <sub>1</sub> |

| RESETB/VPP      | 4 | 15 | OSC <sub>2</sub> |

| VSS             | 5 | 14 | VDD              |

| PB <sub>0</sub> | 6 | 13 | PB7              |

| PB <sub>1</sub> | 7 | 12 | PB <sub>6</sub>  |

| PB <sub>2</sub> | 8 | 11 | PB <sub>5</sub>  |

| PB <sub>3</sub> | 9 | 10 | PB4              |

Package Types : DIP & SOP.

| PA <sub>2</sub> | 1  | 20 | PA <sub>1</sub> |

|-----------------|----|----|-----------------|

| PA <sub>3</sub> | 2  | 19 | PA <sub>0</sub> |

| RTCC            | 3  | 18 | OSC1            |

| RESETB/VPP      | 4  | 17 | OSC2            |

| VSS             | 5  | 16 | VDD             |

| VSS             | 6  | 15 | VDD             |

| PB0             | 7  | 14 | PB7             |

| PB1             | 8  | 13 | PB6             |

| PB2             | 9  | 12 | PB5             |

| PB3             | 10 | 11 | PB4             |

Package Type : SSOP.

| RTCC            | 1 | 14 | OSC <sub>1</sub> |

|-----------------|---|----|------------------|

| RESETB/VPP      | 2 | 13 | OSC <sub>2</sub> |

| VSS             | 3 | 12 | VDD              |

| PB <sub>0</sub> | 4 | 11 | PB7              |

| PB <sub>1</sub> | 5 | 10 | PB <sub>6</sub>  |

| PB <sub>2</sub> | 6 | 9  | PB <sub>5</sub>  |

| PB <sub>3</sub> | 7 | 8  | PB4              |

Package Types : DIP & SOP.

### **PIN** description

| Pin name          | I/O | Description                                                                                             |

|-------------------|-----|---------------------------------------------------------------------------------------------------------|

| RTCC              | I   | External clock input to TMR0 counter                                                                    |

| PA <sub>3-0</sub> | I/O | I/O port                                                                                                |

| PB <sub>7-0</sub> | I/O | I/O port                                                                                                |

| RESETB/VPP        | I   | System reset signal & VPP (High voltage) input  Low voltage: reset mode  High voltage: programming mode |

| OSC <sub>1</sub>  | I   | Oscillator input                                                                                        |

| OSC <sub>2</sub>  | 0   | Oscillator output                                                                                       |

| VDD               | Р   | Power input                                                                                             |

| VSS               | Р   | Ground input                                                                                            |

I: Input; O: Output; I/O: Bi-direction; P: Power

# 3. Control Register

| Name                  | Addr | Bit 7           | Bit 6           | Bit 5            | Bit 4             | Bit 3           | Bit 2           | Bit 1             | Bit 0             |

|-----------------------|------|-----------------|-----------------|------------------|-------------------|-----------------|-----------------|-------------------|-------------------|

| CONFIG (Instruction)  |      |                 |                 |                  |                   | CPT             | WDTE            | FOSC <sub>1</sub> | FOSC <sub>0</sub> |

| SELECT                |      |                 |                 | SUR <sub>0</sub> | EDGE <sub>0</sub> | PSA             | PS <sub>2</sub> | PS <sub>1</sub>   | PS <sub>0</sub>   |

| IAR                   | \$00 |                 |                 |                  | A <sub>4</sub>    | Аз              | A <sub>2</sub>  | <b>A</b> 1        | Ao                |

| TMR0                  | \$01 | D7              | D <sub>6</sub>  | D <sub>5</sub>   | D4                | D <sub>3</sub>  | D <sub>2</sub>  | D <sub>1</sub>    | D <sub>0</sub>    |

| PC                    | \$02 | D7              | D <sub>6</sub>  | D <sub>5</sub>   | D4                | Dз              | D <sub>2</sub>  | D <sub>1</sub>    | D <sub>0</sub>    |

| STATUS                | \$03 |                 |                 | SA <sub>0</sub>  | ТОВ               | PDB             | Z               | DC                | C                 |

| BSR                   | \$04 |                 |                 |                  | D4                | D₃              | D <sub>2</sub>  | D <sub>1</sub>    | D <sub>0</sub>    |

| I/O Port <sub>A</sub> | \$05 |                 |                 |                  |                   | РАз             | PA <sub>2</sub> | PA <sub>1</sub>   | PA <sub>0</sub>   |

| I/O Port <sub>B</sub> | \$06 | PB <sub>7</sub> | PB <sub>6</sub> | PB <sub>5</sub>  | PB <sub>4</sub>   | PB <sub>3</sub> | PB <sub>2</sub> | PB <sub>1</sub>   | PB <sub>0</sub>   |

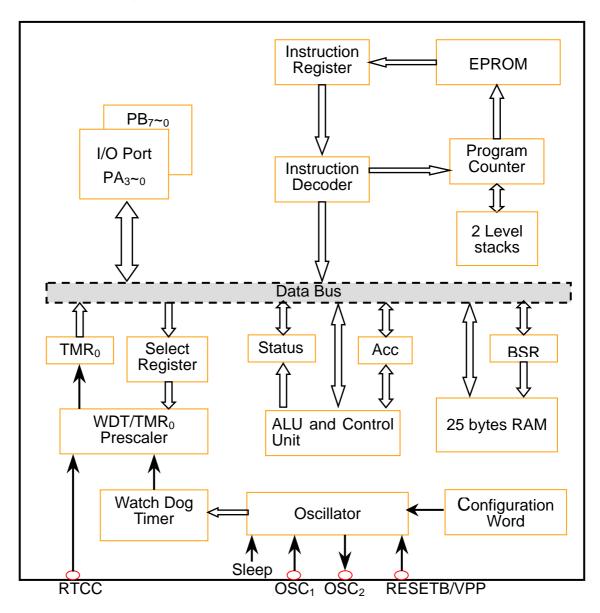

### 4. System Block Diagram

#### 5. Memory Map

TM58PC10 memory is organized into program memory and data memory.

#### **5.1 Program memory**

TM58PC10 allow directly goto any address in 1K memories without limited by page size. In addition, Icall and Igoto instructions are employed to provide flexible addressing mode. TM58PC10 has a 10-bits program counter capable of accessing 1K spaces. If accessing address has over 1K, then the address will map to physical 1K memories, i.e. 1K+M will be mapped to M. A NOP at the reset vector location will cause a restart at address 000h. A simple map to induce illustrate ROM organization is shown in figures 5-1.

Figure 5-1 The ROM Organization

The configuration word is located 800H that contains OSC selection, WDT enable and code protection.(Figure 5-2).

| Bit | Symbol                               |                  | Description      |                              |                     |  |  |  |  |  |

|-----|--------------------------------------|------------------|------------------|------------------------------|---------------------|--|--|--|--|--|

|     |                                      | Bit <sub>1</sub> | Bit <sub>0</sub> | OSC Type                     | Resonance Frequency |  |  |  |  |  |

|     |                                      | 0                | 0                | LP (low speed)               | 32~200K Hz          |  |  |  |  |  |

| 1~0 | FOSC <sub>1</sub> ~FOSC <sub>0</sub> | 0                | 1                | NT <sub>(Normal speed)</sub> | 200K~10M Hz         |  |  |  |  |  |

|     |                                      | 1                | 0                | HS (high speed)              | 10~20M Hz           |  |  |  |  |  |

|     |                                      | 1                | 1                | RC                           | 32K ~ 6M Hz         |  |  |  |  |  |

|     |                                      | WDTE             | : Watc           | hdog enable/disa             | ble control         |  |  |  |  |  |

| 2   | WDTE                                 | 1                | : WDT            |                              |                     |  |  |  |  |  |

|     |                                      | 0                | : WDT            | disable                      |                     |  |  |  |  |  |

|     | CPT: Code Protection bit             |                  |                  |                              |                     |  |  |  |  |  |

| 3   | CPT                                  | 1                | : OFF            |                              |                     |  |  |  |  |  |

|     |                                      | 0                | : ON             |                              |                     |  |  |  |  |  |

Figure 5-2 The Configuration Word

#### 5.2 Data memory

Data memory is composed of special register and general-purpose ram.

TM58PC10 has 25 general-purpose registers that accessed by using a bank select scheme. The special function registers include the program counter (PC), the timer (TMR0) register, the status register, the bank select register, and the I/O port registers. Furthermore, TM58PC10 has 3 auxiliary registers that include indirect addressing register (IAR), the select register (Select) and the I/O direction register (IODIR). The register map is shown in figure 5-3.

|         | Bank <sub>0</sub>                   |

|---------|-------------------------------------|

| 00h     | IAR                                 |

| 01h     | TMR0                                |

| 02h     | PC                                  |

| 03h     | STATUS                              |

| 04h     | BSR                                 |

| 05h     | PORTA                               |

| 06h     | PORTB                               |

| 9+16=25 | General Purpose Register<br>07 – 0F |

| 3110-20 | General Purpose Register<br>10 -1F  |

Figure 5-3 The Register Map

- A. The IAR (indirect addressing register) is not a physical register and is used to assist BSR with indirect addressing. Any instruction attempts to access IAR actually mapping to another address that is pointed by BSR. Since IAR is not a material circuit, user reads IAR itself (BSR=00H) will always return 00h at data bus. Writing to IAR itself will like NOP.

- B. Select register is used to control WDT and TMR0. It has not assigned a specific address in data memory and can only set control bits by "select" instruction, i.e. it is write-only register. The context of accumulator will be sent to the select register by executing the "select" instruction. If select register has never set by program, its default value is 3FH. We drew Figure 5-4 to explain how to set select register.

| Bit | Symbol                           | Description                                       |                                          |                 |                         |                |  |  |  |  |

|-----|----------------------------------|---------------------------------------------------|------------------------------------------|-----------------|-------------------------|----------------|--|--|--|--|

|     |                                  | PS <sub>2</sub>                                   | PS <sub>1</sub>                          | PS <sub>0</sub> | TMR0 rate               | WDT rate       |  |  |  |  |

|     |                                  | 0                                                 | 0                                        | 0               | 1:2                     | 1:1            |  |  |  |  |

|     |                                  | 0                                                 | 0                                        | 1               | 1:4                     | 1:2            |  |  |  |  |

|     |                                  | 0                                                 | 1                                        | 0               | 1:8                     | 1:4            |  |  |  |  |

| 2~0 | PS <sub>2</sub> ~PS <sub>0</sub> | 0                                                 | 1                                        | 1               | 1:16                    | 1:8            |  |  |  |  |

|     |                                  | 1                                                 | 0                                        | 0               | 1:32                    | 1:16           |  |  |  |  |

|     |                                  | 1                                                 | 0                                        | 1               | 1:64                    | 1:32           |  |  |  |  |

|     |                                  | 1                                                 | 1                                        | 0               | 1:128                   | 1:64           |  |  |  |  |

|     |                                  | 1                                                 | 1                                        | 1               | 1:256                   | 1:128          |  |  |  |  |

|     |                                  | PSA: F                                            | Prescal                                  | er assi         | gnment bit              |                |  |  |  |  |

| 3   | PSA                              |                                                   |                                          | •               | gned to WDT             |                |  |  |  |  |

|     |                                  | 0: P                                              | rescale                                  | er assiç        | gned to TMR0            |                |  |  |  |  |

|     |                                  |                                                   |                                          |                 | ce signal edge contro   |                |  |  |  |  |

| 4   | EDGE <sub>0</sub>                | 1:in                                              | cremer                                   | nt wher         | H L transition on e     | external clock |  |  |  |  |

|     |                                  | 0:increment when L H transition on external clock |                                          |                 |                         |                |  |  |  |  |

|     |                                  | SUR <sub>0</sub> :                                | SUR <sub>0</sub> : TMR0 clock source bit |                 |                         |                |  |  |  |  |

| 5   | SUR₀                             | 1: E                                              | xternal                                  | clock           | input                   |                |  |  |  |  |

|     |                                  | 0: (I                                             | nternal                                  | clock)          | /4 or internal instruct | ion cycle      |  |  |  |  |

Figure 5-4 Select Register

- C. The I/O Direction control register is similar to the Select register that is write-only register. To set an I/O port pin as input, the corresponding direction control bit must be high. Similarly, the zero represents output. Any direction control bit can be programmed individually as input or output by using IODIR instruction. If the register is not programmed, than all I/O ports always keep input mode.

- PC (program counter) is a 10-bit wide binary counter and increases itself for every instruction cycle, except the following conditions.

- 1. call, goto, Igoto and Icall: the label will move to PC

- 2. retla, reti and ret: the top value of stack will pop to PC

- Incrementing PC when it changes to the next higher page. It should be noted that the page select bits in the status register would not be changed synchronously. The following Goto, Call, or MOVAM 02H will return to the previous page, unless the page select bits have been updated in program. In order to reduce the complexity of programming, TM58PC10 provides 2 instructions to facilitate subroutine call and branch handling which are LCALL and LGOTO. LCALL and LGOTO can address to anywhere in the ROM, but the page select bits are unnecessary. The attached operands of CALL and GOTO are 8-bit and 9-bit respectively, and so need extra bits (page select bits) to address whole memory. However, LCALL and LGOTO have 10-bit wide operands that are easy to address the total ROM space.

- TMR0 is 8-bit wide binary counter/timer. This register increases by an external signal edge applied to RTCC pin, or by internal instruction cycle. It has the following features.

- A. Readable and writeable

- B. Synchronize with 2 internal clocks

- C. Can use programmable prescaler by setting select register The other details will be described in follow-up chapter.

- Status register contains page select bits, time out bit, power down bit and the status of ALU. Please note that TOB and PDB are controlled by hardware and unchangeable by program.

| Bit | Symbol          | Description                   |                                                                        |                                                        |  |  |  |  |

|-----|-----------------|-------------------------------|------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

|     |                 |                               | Carry and                                                              | d Borrow bit:                                          |  |  |  |  |

|     | _               | ADD                           | ) instruction                                                          | SUB instruction                                        |  |  |  |  |

| 0   | С               | 1: a carry occ<br>0: no carry | curred from the MSB                                                    | 1: no borrow (Note1) 0: a borrow occurred from the MSB |  |  |  |  |

|     |                 |                               | Nibble Carry and                                                       | d Nibble Borrow bit                                    |  |  |  |  |

| 1   | DC              | ADD                           | ) instruction                                                          | SUB instruction                                        |  |  |  |  |

| 1   | DC              |                               | m the low nibble bits                                                  |                                                        |  |  |  |  |

|     |                 | of the resul                  | t occurred                                                             | 0: a borrow from the low nibble bits                   |  |  |  |  |

|     |                 | 0: no carry                   |                                                                        | of the result occurred                                 |  |  |  |  |

|     | _               | Zero bit:                     |                                                                        |                                                        |  |  |  |  |

| 2   | Z               |                               | 1: the result of a logic operation is zero                             |                                                        |  |  |  |  |

|     |                 | 0: the resu                   | the result of a logic operation is not zero ver down flag bit: (Note2) |                                                        |  |  |  |  |

| 3   |                 |                               | <u> </u>                                                               | NADT instruction                                       |  |  |  |  |

| 3   | PD              |                               | wer-on or by the CLR<br>SLEEP instruction                              | TAND I Instruction                                     |  |  |  |  |

|     |                 | Time out flag                 |                                                                        |                                                        |  |  |  |  |

| 4   | $\overline{TO}$ |                               |                                                                        | RWDT or SLEEP instruction                              |  |  |  |  |

| •   | 10              |                               | DT time-overflow                                                       | and i didden in our double                             |  |  |  |  |

|     |                 | Page Location                 |                                                                        |                                                        |  |  |  |  |

|     |                 |                               |                                                                        |                                                        |  |  |  |  |

| 5   | SAo             | 0                             | De                                                                     | 270- (000LL 4FFLI)                                     |  |  |  |  |

| 5   | SA0             | 0                             |                                                                        | age (000H~1FFH)                                        |  |  |  |  |

|     |                 |                               | Pa                                                                     | age1 (200H~3FFH)                                       |  |  |  |  |

Figure 5-5 Status Register

Note1: A SUB instruction is executed by adding the 2's complement of the subtrahend, so C = 1 represents positive result. The Figure 5-5-1 show the relation between C-bit and borrow.

|   |   | BO | )H - | - 50 | )H |    |    |    |    |   |   | 5  | ОН | - B( | ЭН |    |    |    |    |

|---|---|----|------|------|----|----|----|----|----|---|---|----|----|------|----|----|----|----|----|

|   | С | B7 | В6   | B5   | B4 | В3 | B2 | B1 | B0 |   | С | B7 | B6 | B5   | B4 | ВЗ | B2 | B1 | B0 |

|   |   | 1  | 0    | 1    | 1  | 0  | 0  | 0  | 0  |   |   | 0  | 1  | 0    | 1  | 0  | 0  | 0  | 0  |

| + |   | 1  | 0    | 1    | 1  | 0  | 0  | 0  | 0  | + |   | 0  | 1  | 0    | 1  | 0  | 0  | 0  | 0  |

| = | 1 | 0  | 1    | 1    | 0  | 0  | 0  | 0  | 0  | = | 0 | 1  | 0  | 1    | 0  | 0  | 0  | 0  | 0  |

Figure 5-5-1

Note2: The  $\overline{TO}$  and  $\overline{PD}$  bits are active low that can be used to determine different causes of reset. The Figure 5-5-2 illustrates the value of  $\overline{TO}$  and  $\overline{PD}$  after the relative reset events.

| $\overline{TO}$ | $\overline{PD}$ | Reset Event                   |  |  |  |

|-----------------|-----------------|-------------------------------|--|--|--|

| 0               | 0               | WDT time out from sleep mode  |  |  |  |

| 0               | 1               | WDT time out from normal mode |  |  |  |

| 1               | 0               | RESETB reset from sleep       |  |  |  |

| 1               | 1               | Power on reset                |  |  |  |

| Unchanged       | Unchanged       | RESETB reset from normal      |  |  |  |

Figure 5-5-2

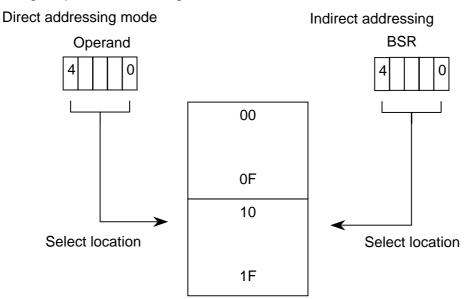

BSR (bank select register) is associated with IAR to indirectly access the data memory. The BSR<4:0> bits are used to select data memory addresses 00h to 1Fh (Bank<sub>0</sub>). The addressing map is shown in Figure 5-6.

Figure 5-6 The Direct and Indirect Addressing Map

Port A~B are programmable I/O ports. Please note that read I/O instruction always read the I/O pin even though the pin is output mode. On reset, all I/O pins were set as input mode until IODIR has been changed.

### 6. Functional Description

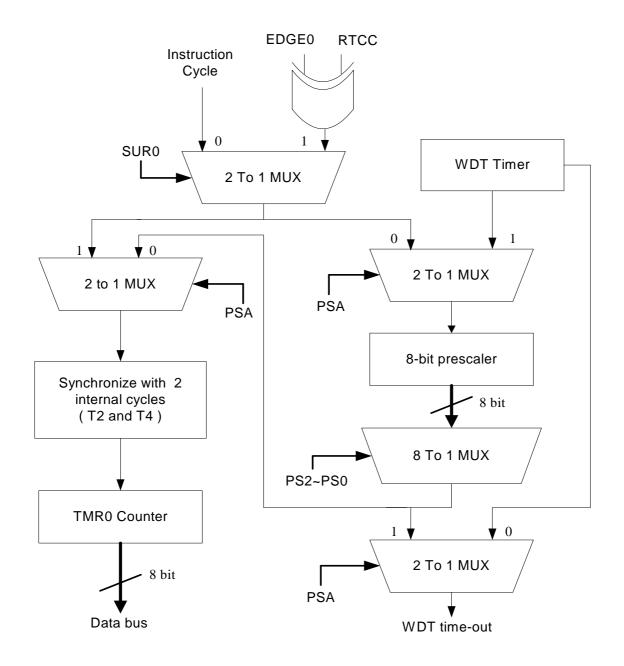

#### 6.1 TMR0 and Watchdog timer

Fig. 6-1 shows the block diagram of the TMR0/WDT prescaler. As shown in the figure, the prescaler register can be a pre-scaler for TMR0 or be a post-scaler for WDT.

Figure 6-1 Block Diagram of the TMR0/WDT Prescaler

The TMR0 is an 8-bit timer/counter. The clock source of TMR0 can come from the instruction clock or the external clock.

- A. To select the instruction clock, the SUR<sub>0</sub> bit of the select register should be clear. When no prescaler is used, TMR0 will increase by 1 at every instruction cycle.

- B. To select the external clock, the SUR<sub>0</sub> bit of the select register should be set. In this mode, TMR0 relies on the EDGE<sub>0</sub> bit to determine that TMR0 is increased by 1 at every falling or rising edge. When an external clock is used for TMR0, a problem must be noted that the external clock synchronizes with internal clock. TM58PC10 synchronizes external clock by sampling internal clock at T2 and T4. If external pulse is smaller than 2 internal cycles, the pulse maybe ignored. Therefore, the external clock must keep stable state (high or low) for at least 2 internal cycles.

The WDT counter is an 8-bit binary counter. The clock source of WDT is provided by an independent on-chip RC oscillator that does not need any external clock. Therefore, the WDT will keep counting even if the chip has slept already. A WDT time-out will restart system and set the time-out flag bit (bit4 of status register) as "0". The WDT time-out period vary with temperature, power voltage and process. This period can be improved via the prescaler. The maximum division ratio can up to 1:128 by setting PS2~PS0 as "111".

The prescaler can be assigned to either the TMR0 or the WDT via the PSA bit. Note that either WDT or TMR0 can employ the prescaler simultaneously. The following Example(1-2) must be executed when changing PSA form TMR0 to the WDT and form WDT to the TMR0 respectively. These examples can avoid an unintended time-out reset.

When the prescaler is assigned to WDT, "CLRWDT" and "SLEEP" instruction will clear the prescaler and the WDT. When the prescaler is assigned to TMR0, the prescaler will be cleared by any instruction that writes to TMR0.

Clrwdt

**Clrm TMR0** ; clear prescaler & TMR0

Movla B'00xx1111'

Select

Clrwdt

Movla B'00xx1xxx'; set prescaler to

desired

**Clrwdt** ; clear prescaler & WDT

Movla B'00xx0xxx'

**Select**; set prescaler to TMR0

; with new rate

Example 1

Changing prescaler form TMR0 to WDT

Example 2 Changing prescaler form WDT to TMR0

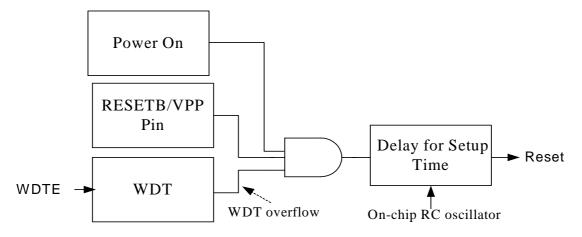

#### 6.2 Reset

TM58PC10 may be reset by one of the following conditions:

- (1) Power-on

- (2) RESETB/VPP pin input a negative pulse

- (3) WDT timer out reset (if enable WDTE).

Figure 6-2 Scheme of the Reset Controller

As shown in the figure 6-2, three reset conditions are listed. In general, we call the first reset-cases as cold reset. The cold reset time may be too short for slow crystals and RC oscillators that require much longer than setup time <sup>(note)</sup> to oscillate.

Note: the setup time is approximately 20ms that will affect due to power voltage, process and temperature variations.

The last two cases are called warm reset. The different reset events will affect registers and ram. The  $\overline{TO}$  and  $\overline{PD}$  bits can be used to determine the type of reset. These relation are listed in figure 6-3

| Address | Name                   | Cold Reset    | Warm Reset             |

|---------|------------------------|---------------|------------------------|

| N/A     | Accumulator            | xxxx xxxx     | pppp pppp              |

| N/A     | IODIR                  | 1111 1111     | 1111 1111              |

| N/A     | Select                 | 11 1111       | 11 1111                |

| 00h     | IAR                    |               |                        |

| 01h     | TMR0                   | xxxx xxxx     | pppp pppp              |

| 02h     | PC                     | 111 1111 1111 | 111 1111 1111          |

| 03h     | STATUS                 | 0001 1xxx     | 000? ?ppp <sup>1</sup> |

| 04h     | BSR                    | 111x xxxx     | 111р рррр              |

| 05h     | PORTA                  | 0000 xxxx     | 0000 pppp              |

| 06h     | PORTB                  | xxxx xxxx     | pppp pppp              |

|         | General<br>Purpose RAM | Xxxx xxxx     | Рррр рррр              |

6-3 RESET CONDITIONS

X: unknown; P: previous data; ?: value depends on condition; -:unimplemented and read as"0".

### 7. Instruction Set

| Mnemonic<br>Operands | Instruction<br>Code (Advance)             | Cycles     | Status<br>Affected | OP-code           |  |  |

|----------------------|-------------------------------------------|------------|--------------------|-------------------|--|--|

| ADDAM M, m           | (M)+(acc) (M)                             | 1          | C, DC, Z           | 10 0101 1MMM MMMM |  |  |

| ADDAM M, a           | (M)+(acc) (acc)                           | 1          | C, DC, Z           | 10 0101 0MMM MMMM |  |  |

| ANDAM M, m           | (M) . (acc) (M)                           | 1          | Z                  | 10 0100 1MMM MMMM |  |  |

| ANDAM M, a           | (M) . (acc) (acc)                         | 1          | Z                  | 10 0100 0MMM MMMM |  |  |

| ANDLA I              | Literal . (acc) (acc)                     | 1          | Z                  | 11 1001 iiii iiii |  |  |

| BCM M, b0            | Clear bit0 of (M)                         | 1          | None               | 00 1100 0MMM MMMM |  |  |

| BCM M, b1            | Clear bit1 of (M)                         | 1          | None               | 00 1100 1MMM MMMM |  |  |

| BCM M, b2            | Clear bit2 of (M)                         | 1          | None               | 00 1101 0MMM MMMM |  |  |

| BCM M, b3            | Clear bit3 of (M)                         | 1          | None               | 00 1101 1MMM MMMM |  |  |

| BCM M, b4            | Clear bit4 of (M)                         | 1          | None               | 00 1110 0MMM MMMM |  |  |

| BCM M, b5            | Clear bit5 of (M)                         | 1          | None               | 00 1110 1MMM MMMM |  |  |

| BCM M, b6            | Clear bit6 of (M)                         | 1          | None               | 00 1111 0MMM MMMM |  |  |

| BCM M, b7            | Clear bit7 of (M)                         | 1          | None               | 00 1111 1MMM MMMM |  |  |

| BSM M, b0            | Set bit0 of (M)                           | 1          | None               | 00 1000 0MMM MMMM |  |  |

| BSM M, b1            | Set bit1 of (M)                           | 1          | None               | 00 1000 1MMM MMMM |  |  |

| BSM M, b2            | Set bit2 of (M)                           | 1          | None               | 00 1001 0MMM MMMM |  |  |

| BSM M, b3            | Set bit3 of (M)                           | 1          | None               | 00 1001 1MMM MMMM |  |  |

| BSM M, b4            | Set bit4 of (M)                           | 1          | None               | 00 1010 0MMM MMMM |  |  |

| BSM M, b5            | Set bit5 of (M)                           | 1          | None               | 00 1010 1MMM MMMM |  |  |

| BSM M, b6            | Set bit6 of (M)                           | 1          | None               | 00 1011 0MMM MMMM |  |  |

| BSM M, b7            | Set bit7 of (M)                           | 1          | None               | 00 1011 1MMM MMMM |  |  |

| BTMSC M, b0          | If bit0 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0100 0MMM MMMM |  |  |

| BTMSC M, b1          | If bit1 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0100 1MMM MMMM |  |  |

| BTMSC M, b2          | If bit2 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0101 0MMM MMMM |  |  |

| BTMSC M, b3          | If bit3 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0101 1MMM MMMM |  |  |

| BTMSC M, b4          | If bit4 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0110 0MMM MMMM |  |  |

| BTMSC M, b5          | If bit5 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0110 1MMM MMMM |  |  |

| BTMSC M, b6          | If bit6 of (M) = 0, skip next instruction | 1 + (skip) | None               | 00 0111 0MMM MMMM |  |  |

| BTMSC M, b7 | If bit7 of (M) = 0, skip next instruction | 1 + (skip) | None   | 00 0111 1MMM MMMM |  |  |

|-------------|-------------------------------------------|------------|--------|-------------------|--|--|

| BTMSS M, b0 | If bit0 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0000 0MMM MMMM |  |  |

| BTMSS M, b1 | If bit1 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0000 1MMM MMMM |  |  |

| BTMSS M, b2 | If bit2 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0001 0MMM MMMM |  |  |

| BTMSS M, b3 | If bit3 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0001 1MMM MMMM |  |  |

| BTMSS M, b4 | If bit4 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0010 0MMM MMMM |  |  |

| BTMSS M, b5 | If bit5 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0010 1MMM MMMM |  |  |

| BTMSS M, b6 | If bit6 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0011 0MMM MMMM |  |  |

| BTMSS M, b7 | If bit7 of (M) = 1, skip next instruction | 1 + (skip) | None   | 00 0011 1MMM MMMM |  |  |

| CALL I      | Call subroutine                           | 2          | None   | 11 0110 iiii iiii |  |  |

| CLRA        | Clear accumulator                         | 1          | Z      | 10 0001 0000 0000 |  |  |

| CLRM M      | Clear memory M                            | 1          | Z      | 10 0001 1MMM MMMM |  |  |

| CLRWDT      | Clear watch-dog register                  | 1          | TO, PO | 10 0000 0000 0001 |  |  |

| COMM M, m   | ~(M) (M)                                  | 1          | Z      | 10 0010 1MMM MMMM |  |  |

| COMM M, a   | ~(M) (acc)                                | 1          | Z      | 10 0010 0MMM MMMM |  |  |

| DECM M, m   | Decrement M to M                          | 1          | Z      | 10 0110 1MMM MMMM |  |  |

| DECM M, a   | (M) - 1 (acc)                             | 1          | Z      | 10 0110 0MMM MMMM |  |  |

| DECMSZ M, m | (M) - 1 (M), skip if (M) = 0              | 1 + (skip) | None   | 10 0111 1MMM MMMM |  |  |

| DECMSZ M, a | (M) - 1 (acc), skip if (M) = 0            | 1 + (skip) | None   | 10 0111 0MMM MMMM |  |  |

| GOTO I      | Goto branch                               | 2          | None   | 11 101i iiii iiii |  |  |

| INCM M, m   | (M) + 1 (M)                               | 1          | Z      | 10 1000 1MMM MMMM |  |  |

| INCM M, a   | (M) + 1 (acc)                             | 1          | Z      | 10 1000 0MMM MMMM |  |  |

| INCMSZ M, m | (M) + 1 $(M)$ , skip if $(M) = 0$         | 1 + (skip) | None   | 10 1001 1MMM MMMM |  |  |

| INCMSZ M, a | (M) + 1 (acc), skip if $(M) = 0$          | 1 + (skip) | None   | 10 1001 OMMM MMMM |  |  |

| IODIR M     | Set i/o direction                         | 1          | None   | 10 0000 0000 0MMM |  |  |

| IORAM M, m  | (M) ior (acc) (M)                         | 1          | Z      | 10 1111 1MMM MMMM |  |  |

| IORAM M, a  | (M) ior (acc) (acc)                       | 1          | Z      | 10 1111 0MMM MMMN |  |  |

| IORLA I     | Literal ior (acc) (acc)                   | 1          | Z      | 11 0011 iiii iiii |  |  |

| LCALL I     | Call subroutine. However, LCALL can addressing 2K address | 2 | None     | O1 Oiii iiii iiii |  |  |

|-------------|-----------------------------------------------------------|---|----------|-------------------|--|--|

| LGOTO I     | Go branch to any address                                  | 2 | None     | O1 1iii iiii iiii |  |  |

| MOVAM m     | Move data form acc to memory                              | 1 | None     | 10 0000 1MMM MMMM |  |  |

| MOVLA I     | Move literal to accumulator                               | 1 | None     | 11 0001 iiii iiii |  |  |

| MOVM M, m   | (M) (M)                                                   | 1 | Z        | 10 0011 1MMM MMMM |  |  |

| MOVM M, a   | (M) (acc)                                                 | 1 | Z        | 10 0011 0MMM MMMN |  |  |

| NOP         | No operation                                              | 1 | None     | 10 0000 0000 0000 |  |  |

| RET         | Return                                                    | 2 | None     | 11 1111 0111 1111 |  |  |

| RETI (note) | Return and enable INTM                                    | 2 | None     | 11 1111 1111 1111 |  |  |

| RETLA I     | Return and move literal to accumulator                    | 2 | None     | 11 1100 iiii iiii |  |  |

| RLM M, m    | Rotate left from m to itself                              | 1 | С        | 10 1100 1MMM MMMM |  |  |

| RLM M, a    | Rotate left from m to acc                                 | 1 | С        | 10 1100 0MMM MMMM |  |  |

| RRM M, m    | Rotate right from m to itself                             | 1 | С        | 10 1110 1MMM MMMM |  |  |

| RRM M, a    | Rotate right from m to acc                                | 1 | С        | 10 1110 0MMM MMMM |  |  |

| SELECT      | Set select register                                       | 1 | None     | 10 0000 0000 0010 |  |  |

| SLEEP       | Enter sleep (saving) mode                                 | 1 | TO, PO   | 10 0000 0000 0011 |  |  |

| SUBAM M, m  | (M)-(acc) (M)                                             | 1 | C, DC, Z | 10 1010 1MMM MMMM |  |  |

| SUBAM M, a  | (M) –(acc) (acc)                                          | 1 | C, DC, Z | 10 1010 0MMM MMMM |  |  |

| SWAPM M, m  | Swap data from m to itself                                | 1 | None     | 10 1101 1MMM MMMM |  |  |

| SWAPM M, a  | Swap data from m to acc                                   | 1 | None     | 10 1101 0MMM MMMM |  |  |

| XORAM M, m  | (M) xor (acc) (M)                                         | 1 | Z        | 10 1011 1MMM MMMM |  |  |

| XORAM M, a  | (M) xor (acc) (acc)                                       | 1 | Z        | 10 1011 0MMM MMMM |  |  |

| XORLA I     | Literal xor (acc) (acc)                                   | 1 | Z        | 11 1000 iiii iiii |  |  |

Note: In TM58PC10 "RETI" instruction don't be used.

#### 8. Electrical Characteristics

### 8.1 Absolute Maximum Ratings

Supply Voltage .... Vss-0.3V to Vss+5.5V Storge Temperature ..... -50 to 125 Input Voltage ..... Vss-0.3V to VDD+0.3V Operating Temperature .... 0 to 70

#### 8.2 DC Characteristics

| Cumbal          | Deremeter                | Test Conditions |               | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------|-----------------|---------------|------|------|------|------|

| Symbol          | Parameter                | VDD             | DD Conditions |      |      |      |      |

| VDD             | Operating Voltage        |                 |               | 2.2  |      | 5.5  | V    |

| V <sub>IH</sub> | Input High Voltage       | 5V              | I/O Port      | 2    |      | VDD  | V    |

| V <sub>IL</sub> | Input Low Voltage        | 5V              | I/O Port      |      |      | 0.8  | V    |

| IDD1            |                          | 5V              | WDT disable   |      | 1    |      | UA   |

| 1001            | Standby Current          | 30              | WDT enable    |      | 10   |      |      |

| I <sub>IL</sub> | Input Leakage<br>Current | 5V              | Vin=VDD, VSS  |      | 1    |      | UA   |

|                 |                          |                 | Voh=4.5V      |      | 9    |      |      |

| I <sub>OH</sub> | I/O Port Driving         | 5V              | Voh=4V        |      | 17   |      | mΑ   |

|                 | Current                  |                 | Voh=3.5V      |      | 23   |      |      |

|                 |                          |                 | Vol=0.5V      |      | 20   |      |      |

| I <sub>OL</sub> | I/O Port Sink            | 5V              | Vol=01V       |      | 35   |      | mΑ   |

|                 | Current                  |                 | Vol=1.5V      |      | 50   |      |      |

#### 8.3 AC Characteristics

|                   |            | Test | Conditions        |     |     |     |        |  |

|-------------------|------------|------|-------------------|-----|-----|-----|--------|--|

| Symbol            | Parameter  | VDD  | Conditions        | Min | Тур | Max | Unit   |  |

| £                 | System     | 5V   | LP Crystal mode   | 32  |     | 200 | Khz    |  |

| f <sub>sys1</sub> | Clock      | 3V   | LP Crystal Illoue | 32  |     | 200 | KIIZ   |  |

| £                 | System     | 5V   | NT Crystal mode   | 0.2 |     | 10  | Mhz    |  |

| f <sub>sys2</sub> | Clock      | 3V   |                   | 0.2 |     | 10  | IVITIZ |  |

| £                 | System     | 5V   | HS Crystal mode   | 10  |     | 20  | Mhz    |  |

| f <sub>sys3</sub> | Clock      | 3V   |                   |     |     |     | IVITIZ |  |

| £                 | System     | 5V   | RC mode           |     |     | 6   | Mhz    |  |

| $f_{sys4}$        | Clock      | 3V   |                   |     |     | 6   | IVITIZ |  |

| T <sub>wdt</sub>  | Watchdog   | 5V   |                   | •   | 20  |     | mS     |  |

|                   | Timer      | 3V   |                   |     | 30  |     | 1115   |  |

| T <sub>rht</sub>  | Reset Hold | 5V   |                   | •   | 20  |     | mS     |  |

|                   | Time       | 3V   | <b>V</b>          |     | 30  |     | 1113   |  |