# **TM59PA20**

User's Manual

Tenx reserves the right to change or discontinue this product without notice.

tenx technology, inc.

# **Contents**

| 1.  | Overview                                                                                                                                                                                                                          | 2                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|     | 1.1. FEATURE 1.2. Clock Scheme and Instruction Cycle 1.3. Addressing Mode 1.4. ALU and Working (W) Register 1.5. STATUS Register 1.6. Interrupt 1.7. Reset 1.8. Power-Down Mode 1.9. System Config Register 1.10. Instruction Set | 5<br>6<br>6<br>7<br>7 |

| 2.  | Control Register                                                                                                                                                                                                                  | . 21                  |

| 3.  | 8-Bit Timer                                                                                                                                                                                                                       | . 38                  |

| 4.  | 8-Bit PWM                                                                                                                                                                                                                         | . 41                  |

| 5.  | 10-Bit PWM                                                                                                                                                                                                                        | . 43                  |

| 6.  | Analog to Digital Converter                                                                                                                                                                                                       | . 45                  |

| 7.  | I/O Ports                                                                                                                                                                                                                         | . 47                  |

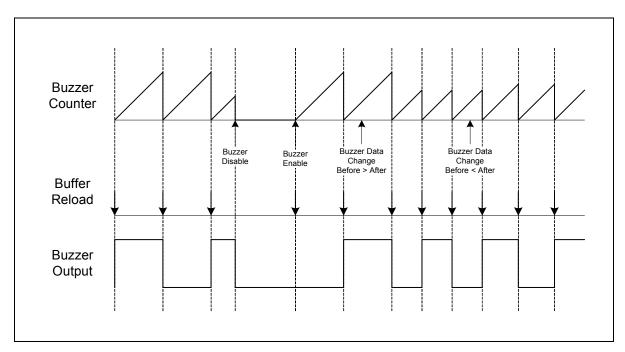

| 8.  | Buzzer Out                                                                                                                                                                                                                        | . 51                  |

| 9.  | Electrical Characteristics                                                                                                                                                                                                        | . 53                  |

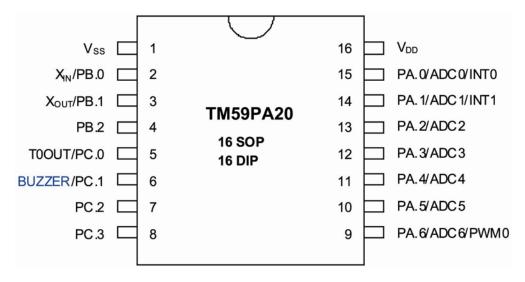

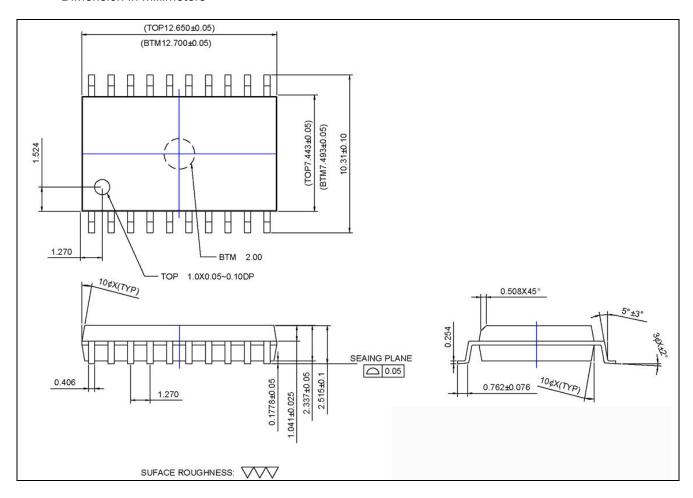

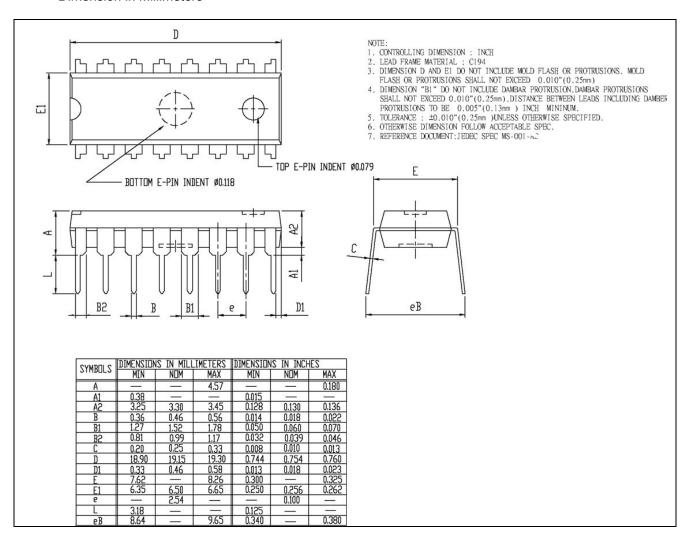

| 10. | Packaging Information                                                                                                                                                                                                             | . 58                  |

1

#### 1. Overview

#### 1.1 FEATURE

- 1. ROM: 2K x 14 bits

- 2. RAM: 192 x 8 bits

- 3. STACK: 6 Levels

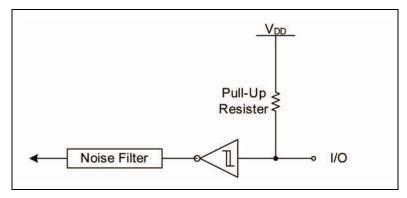

- 4. I/O ports: Three I/O ports (Max 18 pins) and Bit programmable ports

- **5.** Timer/Counter: One 8-bit timer/counter with time interval modes

- 6. Watchdog Timer: On chip WDT based on system oscillator

- 7. Power-On Reset & Watchdog timer overflow Reset & Low Voltage reset

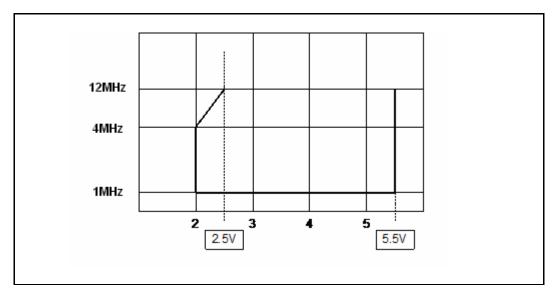

- **8.** Oscillation Frequency:

- 1 MHz to 12 MHz external crystal oscillator

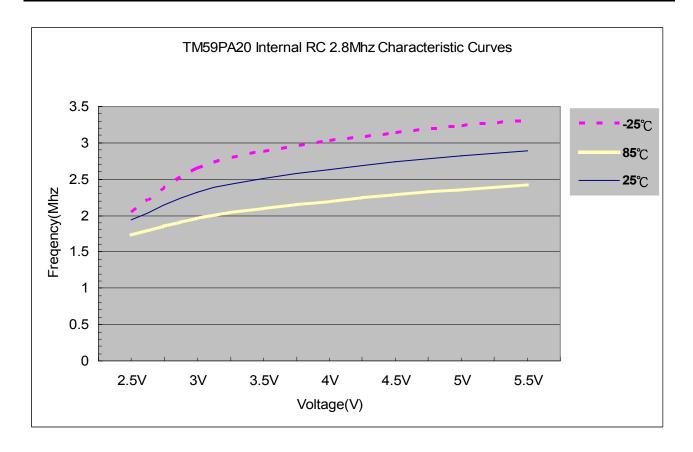

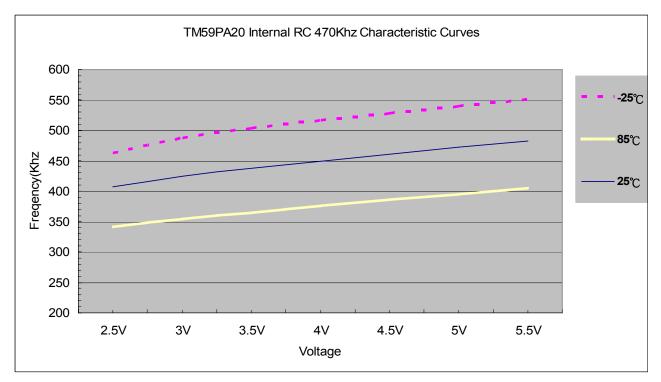

- Internal RC: 2.8 MHz (typ.), 470KHz (typ.) in VDD = 5 V

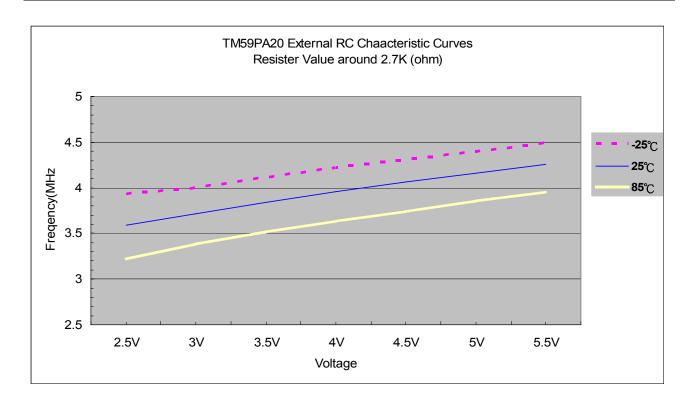

- External RC

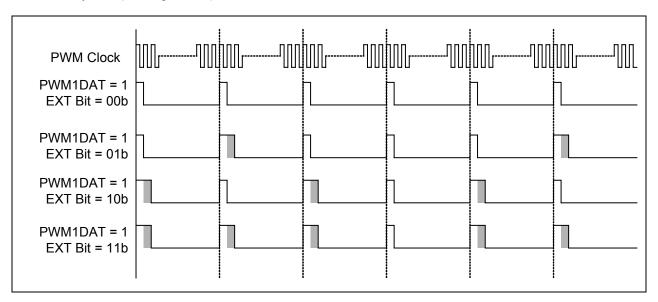

- **9.** High-speed PWM:

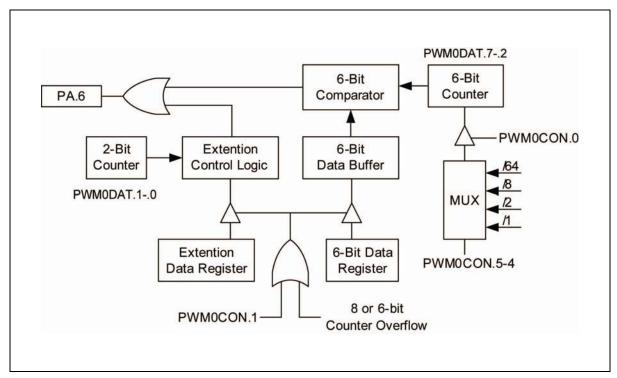

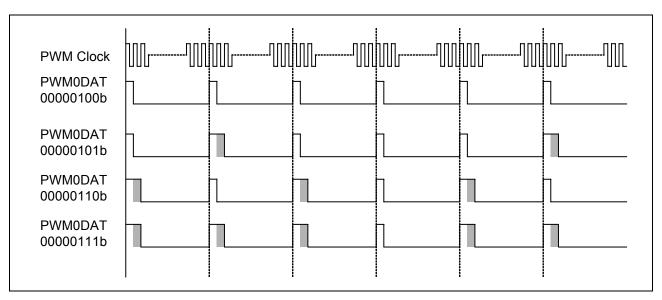

- 8-bit PWM 1-ch, 6-bit base + 2-bit extension (Max: 187 kHz)

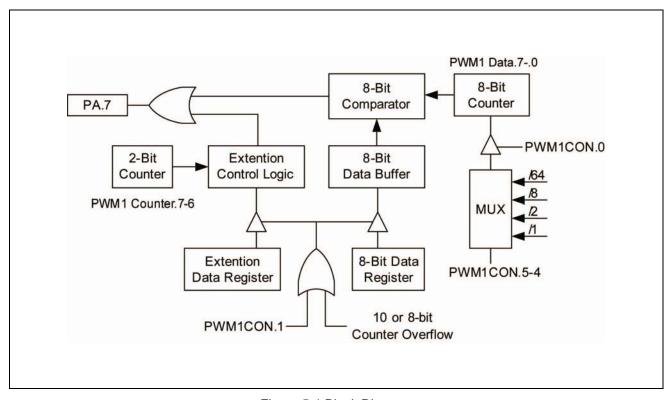

- 10-bit PWM 1-ch, 8-bit base + 2-bit extension (Max: 47 kHz)

- **10.** Operation Voltage: LVR to 5.5V

- 11. Instruction set: 35 Instructions

- **12.** Execution Time: 167 ns at 12 MHz  $f_{OSC}$

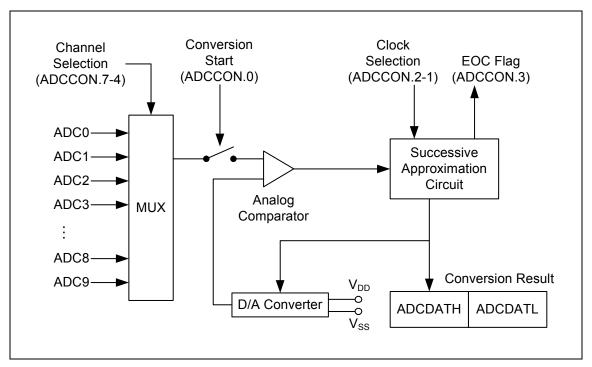

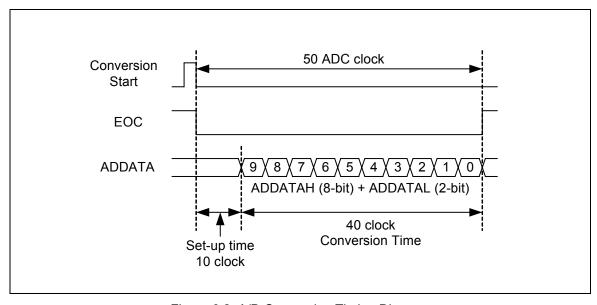

- **13.** A/D Converter: 10-bit conversion resolution with 10-ch analog input pins (MAX)

- **14.** Interrupts: 5 interrupt sources with one vector with one interrupt level

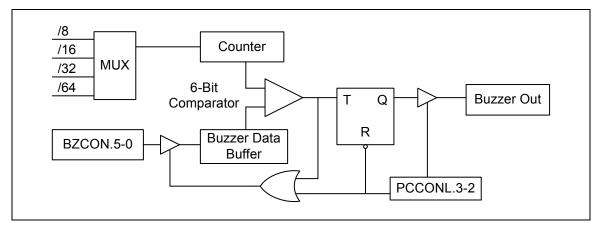

- **15.** Buzzer Out: Frequency Selectable Buzzer Output

- **16.** System Config Option: LVR Level Selection and Clock Source Selection

- 17. Reset vector: 000H

- 18. Interrupt vector: 001H

- 19. Power Down mode

- 20. Package Types:

- 20-SOP, DIP

- 16-SOP, DIP

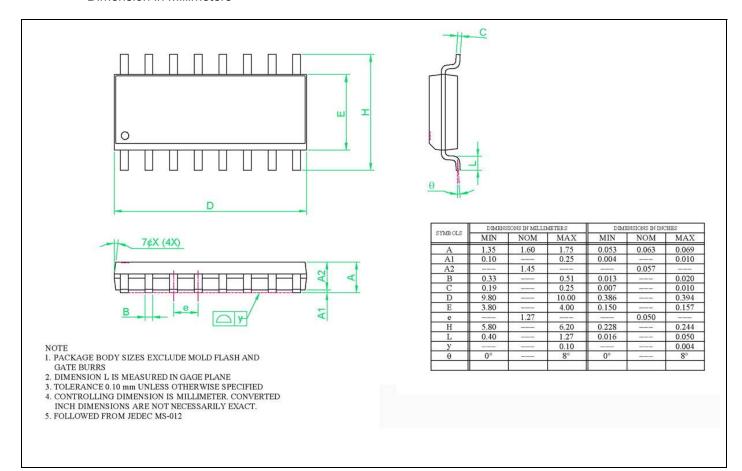

<Figure 1-1. System Block Diagram>

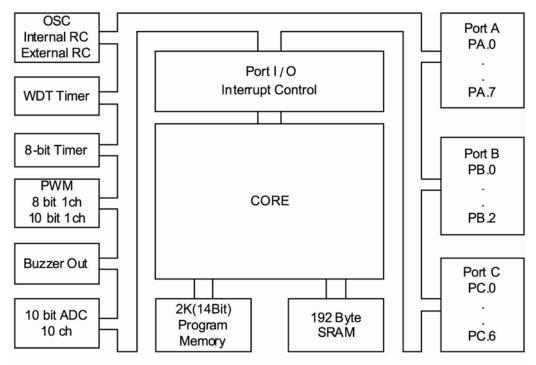

<Figure 1-2. Pin Assignment Diagram \_ Package Types: 20-Pin SOP/DIP>

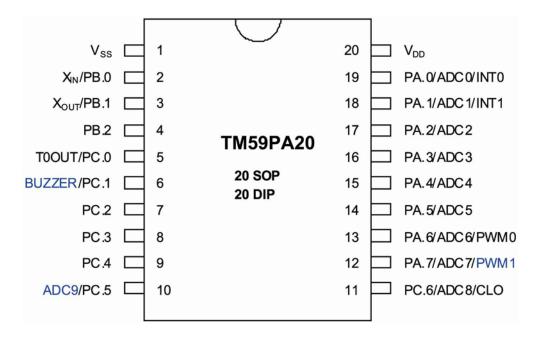

<Figure 1-3. Pin Assignment Diagram \_ Package Types: 16-Pin SOP/DIP>

| Name                 | In/Out | Pin Description                                                                                                                                                                                                    | Shared Function                     |

|----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

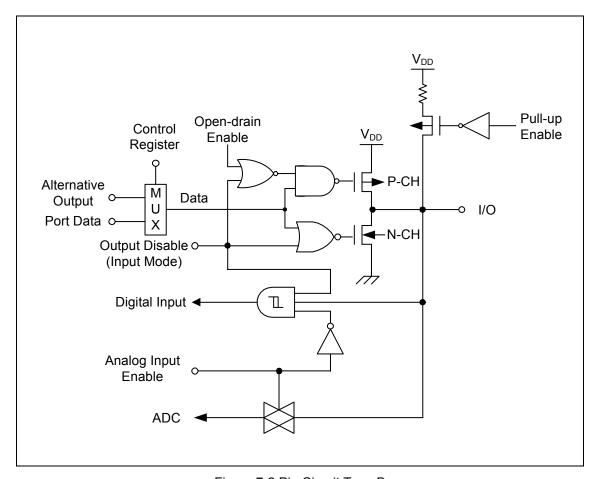

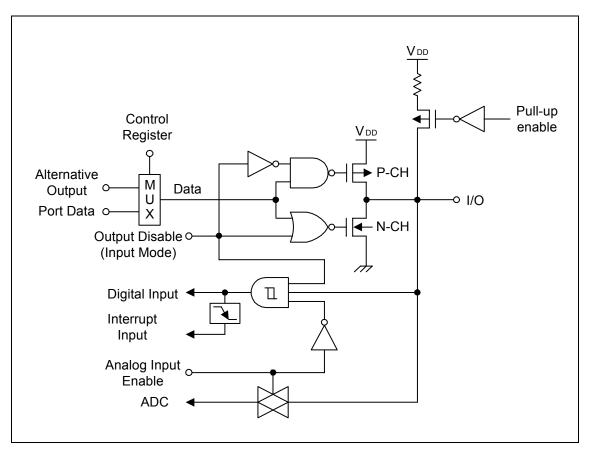

| PA.0-PA.7            | I/O    | Bit-programmable I/O port for Schmitt-trigger input or push-pull output. Pull-up resistors are assignable by software. PortA pins can also be used as A/D converter input, PWM output or external interrupt input. | ADC0-ADC7<br>INT0/INT1<br>PWM0/PWM1 |

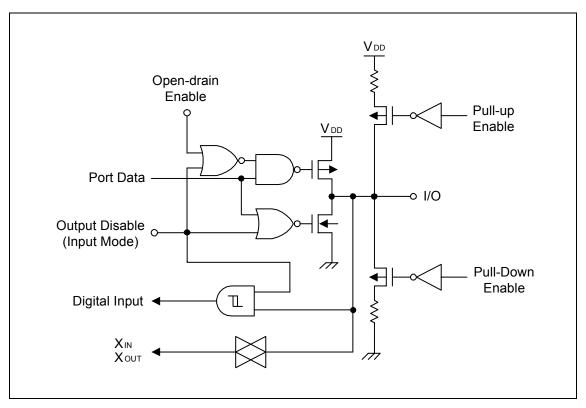

| PB.0–PB.1            | I/O    | Bit-programmable I/O port for Schmitt-trigger input or push-pull, open-drain output. Pull-up resistors or pull-down resistors are assignable by software.                                                          | $X_{IN_{j}}X_{OUT}$                 |

| PB.2                 | I      | Schmitt trigger input port                                                                                                                                                                                         | _                                   |

| PC.0–PC.6            | I/O    | Bit-programmable I/O port for Schmitt-trigger input or push-pull, open-drain output. Pull-up resistors are assignable by software.                                                                                 | ADC8-9/CLO<br>T0OUT/BUZZER          |

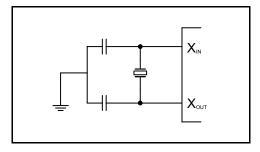

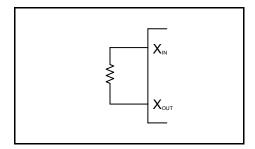

| $X_{IN}$ , $X_{OUT}$ | _      | Crystal/Ceramic, or RC oscillator signal for system clock.                                                                                                                                                         | PB.0-PB.1                           |

| $V_{DD, V_{SS}}$     | Р      | Voltage input pin and ground                                                                                                                                                                                       | _                                   |

| CLO                  | 0      | System clock output port                                                                                                                                                                                           | PC.6                                |

| INT0-INT1            | I      | External interrupt input port                                                                                                                                                                                      | PA.0, PA.1                          |

| PWM0                 | 0      | 8-Bit high speed PWM output                                                                                                                                                                                        | PA.6                                |

| PWM1                 | 0      | 10-Bit high speed PWM output                                                                                                                                                                                       | PA.7                                |

| T0OUT                | 0      | Timer0 match output                                                                                                                                                                                                | PC.0                                |

| ADC0-ADC9            | I      | A/D converter input                                                                                                                                                                                                | PA.0-PA.7<br>PC.5-PC.6              |

<Table 1-1. PIN Description> < I: Input; O: Output; I/O: Bi-direction; P: Power >

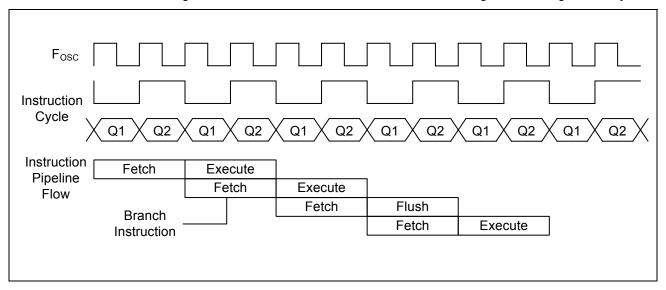

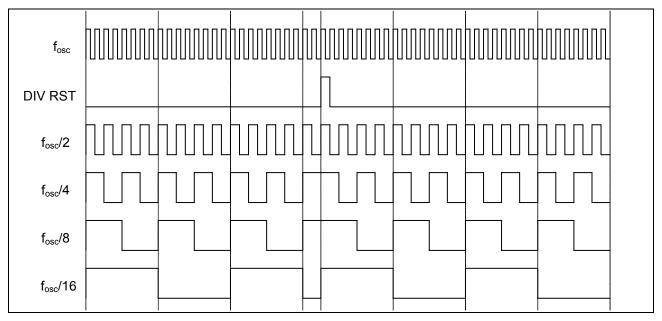

## 1.2 Clock Scheme and Instruction Cycle

The clock input  $(X_{IN})$  is internally divided by two to generate Q1 state and Q2 state for each instruction cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program ROM and latched into the instruction register in Q2. It is then decoded and executed during the following Q1-Q2 cycle.

< Figure 1-4. Clock/Instruction cycle and pipeline >

Branch instructions take two cycle since the fetch instruction is 'flushed' from the pipeline, while the new instruction is being feched and then executed.

# 1.3 Addressing Mode

The Programming Counter is 11-bit wide capable of addressing a 2K x 14 program ROM. As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC value is normally increased by one except the followings. The Reset Vector (000h) and the Interrupt Vector (001h) are provided for PC initialization and Interrupt. For CALL/GOTO instructions, PC loads 11 bits address from instruction word. For RET/RETI/RETLW instructions, PC retrieves its content from the top level STACK. For the other instructions updating PC[7:0], the PC[10:8] keeps unchanged. The STACK is 11-bit wide and 6-level in depth. The CALL instruction and Hardware interrupt will push STACK level in order, While the RET/RETI/RETLW instruction pops the STACK level in order.

The data memory is partitioned into two banks, which contain the General Purpose Data Memory and the Special Function Registers (SFR). STATUS.4 is the bank select bits. Each bank extends up to 7Fh (128 bytes). The lower locations of each bank (00h-1Fh) are reserved for the SFR. Above the SFR is General Purpose Data Memory, implemented as static RAM. SFR area is mirrored in all banks for code reduction and quicker access. The first half of RAM (00h – 3Fh) is bit-addressable.

Data memory can be addressed directly or indirectly. Indirect Addressing is made by INDF register. The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). Reading INDF itself indirectly (FSR=0) will produce 00h. Writing to the INDF register indirectly results in a no-operation.

5

|      | Program Memory    | _  | Data M          | emory           |

|------|-------------------|----|-----------------|-----------------|

| 0000 | Reset Vector      | 00 | Registers, ST   | ATUS 4-0/1      |

| 0001 | Interrupt Vector  |    | Registers, 31   |                 |

|      |                   | 1F | Dit addit       | COSCIDIC        |

|      | Program ROM Page0 | 20 | RAM, STATUS.4=0 | RAM, STATUS.4=1 |

| 7FF  |                   | 7F | Bit addressable | Bit addressable |

< Figure 1-5. Address space >

## 1.4 ALU and Working (W) Register

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. In two-operand instructions, typically one operand is the W register, which is an 8-bit non-addressable register used for ALU operations. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either W register or a file register. Depending on the instruction executed, the ALU may affect the values of Carry (C), Digit Carry (DC), and Zero (Z) Flags in the STATUS register. The C and DC flags operate as a /Borrow and /Digit Borrow, respectively, in subtraction.

## 1.5 STATUS Register

This register contains the arithmetic status of ALU and the Bank select for RAM. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect those bits.

| STATUS      | Bit 7     | Bit 6                                          | Bit 5       | Bit 4                  | Bit 3                                | Bit 2     | Bit 1      | Bit 0  |  |

|-------------|-----------|------------------------------------------------|-------------|------------------------|--------------------------------------|-----------|------------|--------|--|

| Reset Value | _         | 1                                              | _           | 0                      | _                                    | 0         | 0          | 0      |  |

| R/W         | _         | ı                                              | _           | R/W                    | _                                    | R/W       | R/W        | R/W    |  |

| Bit         |           |                                                |             | Descr                  | ription                              |           |            |        |  |

| 7-5         | Not Used  | (Must be                                       | set to 0)   |                        |                                      |           |            |        |  |

|             | SRAM: S   | RAM Ban                                        | k Selection | on Bit                 |                                      |           |            |        |  |

| 4           | 0: Page   |                                                |             |                        |                                      |           |            |        |  |

|             | 1: Page   | 1                                              |             |                        |                                      |           |            |        |  |

| 3           | Not Used  | (Must be                                       | set to 0)   |                        |                                      |           |            |        |  |

|             | Zero Flag | (Z)                                            |             |                        |                                      |           |            |        |  |

| 2           | 0: the re | 0: the result of a logic operation is not zero |             |                        |                                      |           |            |        |  |

|             | 1: the re | sult of a le                                   | ogic opera  | ation is ze            | ero                                  |           |            |        |  |

|             | Decimal ( | Carry Flag                                     | g or Decin  | nal/Borrov             | v Flag (Do                           | C)        |            |        |  |

|             |           | ADD ins                                        | struction   |                        | SUB instruction                      |           |            |        |  |

| 1           | 1: a carr | y from the                                     | e low nibl  | ole bits of            | of 1: no borrow                      |           |            |        |  |

|             | the re    | sult occui                                     | rred        |                        | 0: a borrow from the low nibble bits |           |            |        |  |

| 0: no carry |           |                                                |             | of the result occurred |                                      |           |            |        |  |

|             | Carry Fla | g(C) or Bo                                     | orrow Flag  | g                      |                                      |           |            |        |  |

| 0           |           | ADD ins                                        | struction   |                        | SUB instruction                      |           |            |        |  |

|             | 1: a carr | y occurre                                      | d from the  | e MSB                  | 1: no bo                             | rrow      |            |        |  |

|             | 0: no ca  | rry                                            |             |                        | 0: a bori                            | row occur | red from t | he MSB |  |

<Table 1-2. STATUS — System Flags Register (Address: 03H)>

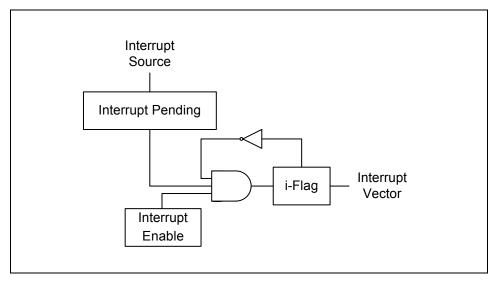

#### 1.6 Interrupt

The TM59PA20 has 1 level, 1 vector and 5 sources. Each interrupt source has its own enable control bit. An interrupt event will set its individual flag. Because TM59PA20 has only 1 vector, there is not a interrupt priority register. The interrupt priority is determined by F/W.

< Figure 1-6. Interrupt Function Diagram >

If the corresponding interrupt enable bit has been set (INTCON), it would trigger CPU to service the interrupt. CPU accepts interrupt in the end of current executed instruction cycle. In the mean while, A "CALL 0001" instruction is inserted to CPU, and the i-flag is set to prevent recursive interrupt nesting. The i-flag is cleared in the instruction after the "RETI" instruction. That is, at least one instruction in main program is executed before service the pending interrupt. The interrupt event is edge trigged. F/W must clear the interrupt event register while serves the interrupt routine.

#### 1.7 Reset

The TM59PA20 can be RESET in four ways.

- Power-On-Reset

- Low Voltage Reset (LVR)

- Watchdog Reset

< Figure 1-7. Reset Circuit Diagram >

After the Power-On-Reset, all system and peripheral control registers are then set to their default hardware Reset values. And the clock source, LVR level is selected by SYSL register value. After the clock source selection, clock oscillation starts, and oscillation stabilization time must be needed. The minimum required oscillation stabilization time is approximately 2.5 ms ( $f_{OSC}$  = 10 MHz). The Low Voltage Reset features static reset when supply voltage is below a reference value. The four levels of reference voltage can be configured in SYSL register.

The Watchdog Timer is disabled after Reset. F/W can use the CLRWDT instruction to clear and enable the Watchdog Timer. If once enabled, the Watchdog Timer overflow and generate a chip reset signal if no

CLRWDT executed in a period of  $2^{21}$  oscillator's cycle (0.25 Second for 8.192MHz crystal). The Watchdog Timer does not work in Power-down mode to provide wake-up function. It is only designed to prevent F/W goes into endless loop.

#### 1.8 Power-Down Mode

The Power-down mode is activated by SLEEP instruction. During the Power-down mode, the crystal clock oscillation stops to minimize power consumption and all the peripherals are not working. Therefore, The Power down mode can be terminated by Reset or enabled external Interrupts (External Interrupt 0, 1). When the Power down mode is released, the clock circuit requires oscillation stabilization time also.

| PWRDN       | Bit 7                                                                                                                                                                 | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|-------|-------|

| Reset Value | _                                                                                                                                                                     | ı                           | _     | _     | ı     | ı     | _     | _     |

| R/W         | _                                                                                                                                                                     | ı                           | _     | _     | ı     | ı     | _     | _     |

| Bit         |                                                                                                                                                                       | Description                 |       |       |       |       |       |       |

| 7-0         | Power Do                                                                                                                                                              | Power Down Control Register |       |       |       |       |       |       |

|             | This register is not physical register. The device can enter STOP mode by writing any value into this register. The SLEEP instruction is equivalent to "MOVWF PWRDN". |                             |       |       |       |       |       |       |

<Table 1-3. PWRDN — Power Down Control Register (Address: 0AH)>

# 1.9 System Config Register

The System Config Register (SYSL) is the ROM option for initial condition of the MCU. The address 2000H is virtual address which is not reachable in F/W. It can be written by MDS and system use only. You can config clock source, LVR reference voltage control by SYSL register. The default value of SYSL is 3FFFh. The 13th bit is code protection selection bit. If write this bit to 0, the data of ROM will be all 3FFFh, when user read ROM.

| NAME        | Bit 13  | Bit 7                         | Bit 6     | Bit 5     | Bit 4     | Bit 3         | Bit 2 | Bit 1 | Bit 0 |

|-------------|---------|-------------------------------|-----------|-----------|-----------|---------------|-------|-------|-------|

| SYSL        | _       | 1                             | _         | -         | _         | -             | 1     | _     | _     |

| Reset Value | 1       | 1                             | 1         | 1         | 1         | 1             | 1     | 1     | 1     |

| Bit         |         |                               |           | D         | escriptio | n             |       |       |       |

| 13          | Code p  | rotection                     | selection | n bit     |           |               |       |       |       |

|             | 1: No p | rotect                        |           |           |           |               |       |       |       |

|             | 0: Code | e protect                     | ion       |           |           |               |       |       |       |

| 7           | Not Us  | ed (Must                      | Set be    | 1')       |           |               |       |       |       |

| 6-5         | CSS1    | CSS0                          | CSS1      | ~0Clock   | Source S  | Selection     | Bit   |       |       |

|             | 0       | 0                             | Extern    | al crysta | I / ceram | nic oscilla   | ator  |       |       |

|             | 0       | 1                             | Extern    | al RC     |           |               |       |       |       |

|             | 1       | 0                             | Interna   | al RC (0. | 47 MHz    | in $V_{DD} =$ | 5 V)  |       |       |

|             | 1       | 1                             | Interna   | al RC (2. | 8 MHz ir  | $V_{DD} = 5$  | (V)   |       |       |

| 4-0         | LVS: L' | LVS: LVR Level Selection Byte |           |           |           |               |       |       |       |

|             | 110     | 001                           | 2.0V      |           |           |               |       |       |       |

|             | 110     | )10                           | 2.3V      |           |           |               |       |       |       |

|             | 100     |                               | 3.0V      |           |           |               |       |       |       |

|             | 011     | 111                           | 3.9V      |           |           |               |       |       |       |

<Table 1-4. SYSL — System Config Register (Address: 2000H)>

#### 1.10 Instruction Set

Each instruction is a 14-bit word divided into an OPCODE, which specified the instruction type, and one or more operands, which further specify the operation of the instruction. The instructions can be categorized as byte-oriented, bit-oriented and literal operations list in the following table.

For byte-oriented instructions, "f" represents address designator and "d" represents destination designator. The address designator is used to specify which address in Program memory is to be used by the instruction. The destination designator specifies where the result of the operation is to be placed. If "d" is "0", the result is placed in the W register. If "d" is "1", the result is placed in the address specified in the instruction.

For bit-oriented instructions, "b" represents a bit field designator, which selects the number of the bit affected by the operation, while "f" represents the address designator. For literal operations, "k" represents the literal or constant value.

| Field    | Description                                                         |

|----------|---------------------------------------------------------------------|

| f        | Register File Address                                               |

| b        | Bit address                                                         |

| k        | Literal. Constant data or label                                     |

| d        | Destination selection field. 0 : Working register 1 : Register file |

| W        | Working Register                                                    |

| Z        | Zero Flag                                                           |

| С        | Carry Flag                                                          |

| DC       | Decimal Carry Flag                                                  |

| PC       | Program Counter                                                     |

| TOS      | Top Of Stack                                                        |

| GIE      | Global Interrupt Enable Flag (i-Flag)                               |

| ()       | Contents                                                            |

|          | Bit Field                                                           |

| <b>←</b> | Assign direction                                                    |

< Table 1-5. OP-CODE Field Description >

| Mnemonic                                |     | Op Code          | Cycle       | Flag Affect     | Description                                   |  |  |  |

|-----------------------------------------|-----|------------------|-------------|-----------------|-----------------------------------------------|--|--|--|

| Byte-Oriented File Register Instruction |     |                  |             |                 |                                               |  |  |  |

| ADDWF                                   | f,d | 00 0111 dfff fff |             | C,DC,Z          | Add W and "f"                                 |  |  |  |

| ANDWF                                   | f,d | 00 0101 dfff fff | f 1         | Z               | AND W with "f"                                |  |  |  |

| CLRF                                    | f   | 00 0001 1fff fff | f 1         | Z               | Clear "f"                                     |  |  |  |

| CLRW                                    |     | 00 0001 0100 000 | 1           | Z               | Clear W                                       |  |  |  |

| COMF                                    | f,d | 00 1001 dfff fff | f 1         | Z               | Complement "f"                                |  |  |  |

| DECF                                    | f,d | 00 0011 dfff fff | f 1         | Z               | Decrement "f"                                 |  |  |  |

| DECFSZ                                  | f,d | 00 1011 dfff fff | f 1 or 2    | -               | Decrement "f", skip if zero                   |  |  |  |

| INCF                                    | f,d | 00 1010 dfff fff | f 1         | Z               | Increment "f"                                 |  |  |  |

| INCFSZ                                  | f,d | 00 1111 dfff fff | f 1 or 2    | -               | Increment "f", skip if zero                   |  |  |  |

| IORWF                                   | f,d | 00 0100 dfff fff | f 1         | Z               | OR W with "f"                                 |  |  |  |

| MOVFW                                   | f   | 00 1000 Offf fff | f 1         | -               | Move "f" to "w"                               |  |  |  |

| MOVWF                                   | f   | 00 0000 1fff fff | f 1         | -               | Move W to "f"                                 |  |  |  |

| RLF                                     | f,d | 00 1101 dfff fff | f 1         | С               | Rotate left "f" through carry                 |  |  |  |

| RRF                                     | f,d | 00 1100 dfff fff | f 1         | С               | Rotate right "f" through carry                |  |  |  |

| SUBWF                                   | f,d | 00 0010 dfff fff | f 1         | C,DC,Z          | Subtract W from "f"                           |  |  |  |

| SWAPF                                   | f,d | 00 1110 dfff fff | f 1         | -               | Swap nibbles in "f"                           |  |  |  |

| TESTZ                                   | f   | 00 1000 1fff fff | f 1         | Z               | Test if "f" is zero                           |  |  |  |

| XORWF                                   | f,d | 00 0110 dfff fff | f 1         | Z               | XOR W with "f"                                |  |  |  |

|                                         |     | Bit-Orien        | ted File Re | egister Instru  | ction                                         |  |  |  |

| BCF                                     | f,b | 01 000b bbff fff | f 1         | -               | Clear "b" bit of "f"                          |  |  |  |

| BSF                                     | f,b | 01 001b bbff fff | f 1         | -               | Set "b" bit of "f"                            |  |  |  |

| BTFSC                                   | f,b | 01 010b bbff fff | f 1 or 2    | -               | Test "b" bit of "f", skip if clear            |  |  |  |

| BTFSS                                   | f,b | 01 011b bbff fff | f 1 or 2    | -               | Test "b" bit of "f", skip if set              |  |  |  |

|                                         |     | Litera           | l and Cont  | trol Instructio |                                               |  |  |  |

| ADDLW                                   | k   | 01 1100 kkkk kkk | k 1         | C,DC,Z          | Add Literal "k" and W                         |  |  |  |

| ANDLW                                   | k   | 01 1011 kkkk kkk | k 1         | Z               | AND Literal "k" with W                        |  |  |  |

| CALL                                    | k   | 10 0kkk kkkk kkk | k 2         | -               | Call subroutine "k"                           |  |  |  |

| CLRWDT                                  |     | 00 0000 1000 100 | 1 1         | -               | Clear and enable Watch Dog Timer              |  |  |  |

| GOTO                                    | k   | 11 Okkk kkkk kkk | k 2         | -               | Jump to branch "k"                            |  |  |  |

| IORLW                                   | k   | 01 1010 kkkk kkk | k 1         | Z               | OR Literal "k" with W                         |  |  |  |

| MOVLW                                   | k   | 01 1001 kkkk kkk | k 1         | -               | Move Literal "k" to W                         |  |  |  |

| NOP                                     |     | 00 0000 0000 000 | 1           | -               | No operation                                  |  |  |  |

| RET                                     |     | 00 0000 0100 000 |             | -               | Return from subroutine                        |  |  |  |

| RETI                                    |     | 00 0000 0110 000 | _           | -               | Return from interrupt                         |  |  |  |

| RETLW                                   | k   | 01 1000 kkkk kkk | k 2         | -               | Return with Literal "k" in W                  |  |  |  |

| SLEEP                                   |     | 00 0000 1000 101 | ) <b>1</b>  | -               | Go into standby mode, Clock oscillation stops |  |  |  |

| XORLW                                   | k   | 01 1111 kkkk kkk | k 1         | Z               | XOR Literal "k" with W                        |  |  |  |

< Table 1-6. Instruction Summary >

| ADDLW  | Add Literal "k" and W |

|--------|-----------------------|

| ADDLII | Add Elicial R alid W  |

$\begin{array}{lll} \text{Syntax} & \text{ADDLW k} \\ \text{Operands} & \text{k}: 00\text{h} \sim \text{FFh} \\ \text{Operation} & (\text{W}) \leftarrow (\text{W}) + \text{k} \\ \text{Status Affected} & \text{C, DC, Z} \\ \end{array}$

OP-Code 01 1100 kkkk kkkk

Description The contents of the W register are added to the eight-bit literal 'k' and the

result is placed in the W register.

Cycle 1

Example ADDLW 0x15 B: W = 0x10

A: W = 0x25

#### ADDWF Add W and 'f'

Syntax ADDWF f [,d] Operands f:  $00h \sim 7Fh d: 0, 1$ Operation (Destination)  $\leftarrow$  (W) + (f)

Status Affected C, DC, Z

OP-Code 00 0111 dfff ffff

Description Add the contents of the W register with register 'f'. If 'd' is 0, the result is

stored in the W register. If 'd' is 1, the result is stored back in register 'f'.

Cycle 1

Example ADDWF FSR, 0 B: W = 0x17, FSR = 0xC2

A: W = 0xD9, FSR = 0xC2

#### ANDLW Logical AND Literal "k" with W

Syntax ANDLW k

Operands k:00h~FFh

Operation  $(W) \leftarrow (W)$  'AND' (f)

Status Affected Z

OP-Code 01 1011 kkkk kkkk

Description The contents of W register are AND'ed with the eight-bit literal 'k'. The

result is placed in the W register.

Cycle 1

Example ANDLW 0x5F B: W = 0xA3

A: W = 0x03

#### ANDWF AND W with f

Syntax ANDWF f [,d]

Operands  $f: 00h \sim 7Fh \quad d: 0, 1$ Operation (Destination)  $\leftarrow$  (W) 'AND' (f)

Status Affected Z

OP-Code 00 0101 dfff ffff

Description AND the W register with register 'f'. If 'd' is 0, the result is stored in the W

11

register. If 'd' is 1, the result is stored back in register 'f'.

Cycle 1

Example ANDWF FSR, 1 B: W = 0x17, FSR = 0xC2

A: W = 0x17, FSR = 0x02

| BCF                                                                          | Clear "b" bit of "f"                                                                                                                                 |                                                                                          |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Syntax Operands Operation Status Affected OP-Code Description Cycle Example  | BCF f [,b]<br>f: 00h ~ 3Fh b: 0 ~ 7<br>(f.b) $\leftarrow$ 0<br>-<br>01 000b bbff ffff<br>Bit 'b' in register 'f' is cleared.<br>1<br>BCF FLAG_REG, 7 | B : FLAG_REG = 0xC7<br>A : FLAG_REG = 0x47                                               |

| BSF                                                                          | Set "b" bit of "f"                                                                                                                                   |                                                                                          |

| Syntax Operands Operation Status Affected OP-Code Description Cycle Example  | BSF f [,b]<br>f:00h ~ 3Fh b:0 ~ 7<br>(f.b) ← 1<br>-<br>01 001b bbff ffff<br>Bit 'b' in register 'f' is set.<br>1<br>BSF FLAG_REG, 7                  | B : FLAG_REG = 0x0A<br>A : FLAG_REG = 0x8A                                               |

| BTFSC                                                                        | Test 'b' bit of 'f', skip if                                                                                                                         | clear(0)                                                                                 |

| Syntax Operands Operation Status Affected OP-Code Description  Cycle Example |                                                                                                                                                      | n the next instruction is executed. If bit 'b' in instruction is discarded, and a NOP is |

| BTFSS                                                                        | Test "b" bit of "f", skip                                                                                                                            | if set(1)                                                                                |

| Syntax Operands Operation Status Affected OP-Code Description  Cycle Example |                                                                                                                                                      | n the next instruction is executed. If bit 'b' in instruction is discarded, and a NOP is |

**CALL** Call subroutine "k" Syntax CALL k **Operands** K: 00h ~ 7FFh Operation Operation: TOS  $\leftarrow$  (PC)+ 1, PC.10 $\sim$ 0  $\leftarrow$  k Status Affected OP-Code 10 0kkk kkkk kkkk Call Subroutine. First, return address (PC+1) is pushed onto the stack. Description The eleven-bit immediate address is loaded into PC bits <10:0>. CALL is a two-cycle instruction. Cycle Example LABEL1 CALL SUB1 B: PC = LABEL1 A: PC = SUB1, TOS = LABEL1+1

**CLRF** Clear f CLRF f Syntax f: 00h ~ 7Fh Operands (f)  $\leftarrow$  00h, Z  $\leftarrow$  1 Operation Status Affected Ζ OP-Code 00 0001 1fff ffff Description The contents of register 'f' are cleared and the Z bit is set. Cycle  $B: FLAG_REG = 0x5A$ Example CLRF FLAG\_REG A:  $FLAG_REG = 0x00$ , Z = 1

**CLRW** Clear W Syntax **CLRW** Operands Operation  $(W) \leftarrow 00h, Z \leftarrow 1$ Status Affected OP-Code 00 0001 0100 0000 W register is cleared and Zero bit (Z) is set. Description Cycle Example **CLRW** B:W=0x5A

A: W = 0x00, Z = 1

CLRWDT Clear Watchdog Timer

SyntaxCLRWDTOperands-OperationWDTE ← 00hStatus Affected-

OP-Code 00 0000 1000 1001

Description CLRWDT instruction enables and resets the Watchdog Timer.

Cycle 1

Example CLRWDT B : WDT counter = ?

A : WDT counter = 0x00

| COMF                       | Complement f                                                                                                                                   |                                              |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Syntax<br>Operands         | COMF f [,d]<br>f : 00h ~ 7Fh, d : 0, 1                                                                                                         |                                              |  |

| Operation                  | $(\text{destination}) \leftarrow (\bar{f})$                                                                                                    |                                              |  |

| Status Affected<br>OP-Code | Z<br>00 1001 dfff ffff                                                                                                                         |                                              |  |

| Description                | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |                                              |  |

| Cycle                      | 1                                                                                                                                              | · ·                                          |  |

| Example                    | COMF REG1,0                                                                                                                                    | B : REG1 = 0x13<br>A : REG1 = 0x13, W = 0xEC |  |

| DECF            | Decrement f                       |                                                   |

|-----------------|-----------------------------------|---------------------------------------------------|

| Syntax          | DECF f [,d]                       |                                                   |

| Operands        | f: 00h ~ 7Fh, d: 0, 1             |                                                   |

| Operation       | (destination) ← (f) - 1           |                                                   |

| Status Affected | Z                                 |                                                   |

| OP-Code         | 00 0011 dfff ffff                 |                                                   |

| Description     | Decrement register 'f'. If 'd' is | 0, the result is stored in the W register. If 'd' |

|                 | is 1, the result is stored back i | n register 'f'.                                   |

| Cycle           | 1                                 | •                                                 |

| Example         | DECF CNT, 1                       | B : $CNT = 0x01, Z = 0$                           |

|                 |                                   | A : CNT = 0x00, Z = 1                             |

| DECFSZ          | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax          | DECFSZ f [,d]                                                                                                                                                                                                                                                                                         |

| Operands        | f: 00h ~ 7Fh, d: 0, 1                                                                                                                                                                                                                                                                                 |

| Operation       | (destination) $\leftarrow$ (f) - 1, skip next instruction if result is 0                                                                                                                                                                                                                              |

| Status Affected | -                                                                                                                                                                                                                                                                                                     |

| OP-Code         | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                     |

| Description     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2 cycle instruction. |

| Cycle           | 1 or 2                                                                                                                                                                                                                                                                                                |

| Example         | LABEL1 DECFSZ CNT, 1 B : PC = LABEL1                                                                                                                                                                                                                                                                  |

|                 | GOTO LOOP A: CNT = CNT – 1                                                                                                                                                                                                                                                                            |

|                 | CONTINUE if CNT=0, PC = CONTINUE                                                                                                                                                                                                                                                                      |

|                 | if CNT≠0, PC = LABEL1+1                                                                                                                                                                                                                                                                               |

|                 |                                                                                                                                                                                                                                                                                                       |

| GOTO            | <b>Unconditional Branch</b> |                                             |

|-----------------|-----------------------------|---------------------------------------------|

| Syntax          | GOTO k                      |                                             |

| Operands        | k : 00h ~ 7FFh              |                                             |

| Operation       | PC.10~0 ← k                 |                                             |

| Status Affected | -                           |                                             |

| OP-Code         | 11 Okkk kkkk kkkk           |                                             |

| Description     | GOTO is an unconditional be | ranch. The 11-bit immediate value is loaded |

|                 | into PC bits <10:0>. GOTO i | s a two-cycle instruction.                  |

| Cycle           | 2                           | •                                           |

| Example         | LABEL1 GOTO SUB1            | B : PC = LABEL1                             |

| -               |                             | A · PC = SUB1                               |

14

| INCF            | Increment f                                                                                                                                                |                           |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Syntax          | INCF f [,d]                                                                                                                                                |                           |

| Operands        | f : 00h ~ 7Fh                                                                                                                                              |                           |

| Operation       | $(destination) \leftarrow (f) + 1$                                                                                                                         |                           |

| Status Affected | Ž                                                                                                                                                          |                           |

| OP-Code         | 00 1010 dfff ffff                                                                                                                                          |                           |

| Description     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |                           |

| Cycle           | 1                                                                                                                                                          | •                         |

| Example         | INCF CNT, 1                                                                                                                                                | B: CNT = $0xFF$ , $Z = 0$ |

| •               |                                                                                                                                                            | A: $CNT = 0x00, Z = 1$    |

| INCFSZ | Increment f, | Skip | if 0 |

|--------|--------------|------|------|

|        |              |      |      |

| Syntax          | NCFSZ f [,d]                                                                                                                                                                                                                                                             |          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Operands        | : 00h ~ 7Fh, d : 0, 1                                                                                                                                                                                                                                                    |          |

| Operation       | destination) ← (f) + 1, skip next instruction if result is 0                                                                                                                                                                                                             |          |

| Status Affected | , ,, ,                                                                                                                                                                                                                                                                   |          |

| OP-Code         | 0 1111 dfff ffff                                                                                                                                                                                                                                                         |          |

| Description     | he contents of register 'f' are incremented. If 'd' is 0, the result is the W register. If 'd' is 1, the result is placed back in register 'f' esult is 1, the next instruction is executed. If the result is 0, a NC executed instead, making it a 2 cycle instruction. | . If the |

| Cycle           | or 2                                                                                                                                                                                                                                                                     |          |

| Example         | ABEL1 INCFSZ CNT, 1 B : PC = LABEL1                                                                                                                                                                                                                                      |          |

|                 | GOTO LOOP A: CNT = CNT + 1                                                                                                                                                                                                                                               |          |

|                 | CONTINUE if CNT=0, PC = CONTINUI                                                                                                                                                                                                                                         | E        |

# IORLW Inclusive OR Literal with W

| Syntax          | IORLW k                                      |                                                                       |

|-----------------|----------------------------------------------|-----------------------------------------------------------------------|

| Operands        | k : 00h ~ FFh                                |                                                                       |

| Operation       | $(W) \leftarrow (W) OR k$                    |                                                                       |

| Status Affected | Ž                                            |                                                                       |

| OP-Code         | 01 1010 kkkk kkkk                            |                                                                       |

| Description     | The contents of the versult is placed in the | W register is OR'ed with the eight-bit literal 'k'. The e W register. |

| Cycle           | 1                                            |                                                                       |

| Example         | IORLW 0x35                                   | B : W = 0x9A<br>A : W = 0xBF, Z = 0                                   |

#### IORWF Inclusive OR W with f

| Syntax          | IORWF f [,d]                                                                                                                                                |                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Operands        | f: 00h ~ 7Fh, d: 0, 1                                                                                                                                       |                                                                   |

| Operation       | (destination) ← (W) OR                                                                                                                                      | k                                                                 |

| Status Affected | Ż                                                                                                                                                           |                                                                   |

| OP-Code         | 00 0100 dfff ffff                                                                                                                                           |                                                                   |

| Description     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |                                                                   |

| Cycle           | 1                                                                                                                                                           | •                                                                 |

| Example         | IORWF RESULT, 0                                                                                                                                             | B : RESULT = 0x13, W = 0x91<br>A : RESULT = 0x13, W = 0x93, Z = 0 |

if CNT≠0, PC = LABEL1+1

| MOVFW           | Move f to W                                         |                                     |

|-----------------|-----------------------------------------------------|-------------------------------------|

| Syntax          | MOVFW f                                             |                                     |

| Operands        | f : 00h ~ 7Fh                                       |                                     |

| Operation       | $(W) \leftarrow (f)$                                |                                     |

| Status Affected | <del>-</del>                                        |                                     |

| OP-Code         | 00 1000 Offf ffff                                   |                                     |

| Description     | The contents of register f are moved to W register. |                                     |

| Cycle           | 1                                                   | •                                   |

| Example         | MOVF FSR, 0                                         | B:W=?                               |

| •               |                                                     | A: W $\leftarrow$ f, if W = 0 Z = 1 |

# MOVLW Move Literal to W

|                 | =                                          |                                                 |

|-----------------|--------------------------------------------|-------------------------------------------------|

| Syntax          | MOVLW k                                    |                                                 |

| Operands        | k : 00h ~ FFh                              |                                                 |

| Operation       | (W) ← k                                    |                                                 |

| Status Affected | -                                          |                                                 |

| OP-Code         | 01 1001 kkkk kkkk                          |                                                 |

| Description     | The eight-bit literal 'k' assemble as 0's. | is loaded into W register. The don't cares will |

| Cycle           | 1                                          |                                                 |

| Example         | MOVLW 0x5A                                 | B : W = ?                                       |

|                 |                                            | A:W=0x5A                                        |

|                 |                                            |                                                 |

#### MOVWF Move W to f

| MOVWE           | MOVE WITO I                                |                                |  |

|-----------------|--------------------------------------------|--------------------------------|--|

| Syntax          | MOVWF f                                    |                                |  |

| Operands        | f : 00h ~ 7Fh                              |                                |  |

| Operation       | $(f) \leftarrow (W)$                       |                                |  |

| Status Affected | d -                                        |                                |  |

| OP-Code         | 00 0000 1fff ffff                          |                                |  |

| Description     | Move data from W register to register 'f'. |                                |  |

| Cycle           | 1                                          |                                |  |

| Example         | MOVWF REG1                                 | B : REG1 = $0xFF$ , W = $0x4F$ |  |

|                 |                                            | A : REG1 = $0x4F$ , W = $0x4F$ |  |

# NOP No Operation

| Syntax          | NOP               |

|-----------------|-------------------|

| Operands        | -                 |

| Operation       | No Operation      |

| Status Affected | Z                 |

| OP-Code         | 00 0000 0000 0000 |

| Description     | No Operation      |

| Cycle           | 1                 |

| Example         | NOP -             |

| •               |                   |

| RETI            | Return from Interrupt                                                  |                                              |

|-----------------|------------------------------------------------------------------------|----------------------------------------------|

| Syntax          | RETI                                                                   |                                              |

| Operands        | -                                                                      |                                              |

| Operation       | PC ← TOS, GIE ← 1                                                      |                                              |

| Status Affected | -<br>-                                                                 |                                              |

| OP-Code         | 00 0000 0110 0000                                                      |                                              |

| Description     | Return from Interrupt. Stack is POPed and Top-of-Stack (TOS) is loaded |                                              |

|                 | in to the PC. Interrupts a                                             | re enabled. This is a two-cycle instruction. |

| Cycle           | 2                                                                      | ·                                            |

| Example         | RETFIE                                                                 | A : PC = TOS, GIE = 1                        |

#### RETLW Return with Literal in W

| KLILVV          | Retuin With Literal in W                 |                                                                                       |

|-----------------|------------------------------------------|---------------------------------------------------------------------------------------|

| Syntax          | RETLW k                                  |                                                                                       |

| Operands        | k : 00h ~ FFh                            |                                                                                       |

| Operation       | $PC \leftarrow TOS$ , $(W) \leftarrow k$ |                                                                                       |

| Status Affected | -                                        |                                                                                       |

| OP-Code         | 01 1000 kkkk kkkk                        |                                                                                       |

| Description     | •                                        | he eightbit literal 'k'. The program counter ack (the return address). This is a two- |

| Cycle           | 2                                        |                                                                                       |

| Example         | CALL TABLE                               | B: $W = 0x07$                                                                         |

|                 | :                                        | A:W = value of k8                                                                     |

|                 | TABLE ADDWF PCL,1                        |                                                                                       |

|                 | RETLW k1                                 |                                                                                       |

|                 | RETLW k2                                 |                                                                                       |

|                 | :                                        |                                                                                       |

|                 | RETLW kn                                 |                                                                                       |

|                 |                                          |                                                                                       |

| RET | Poturn | from   | <b>Subroutine</b> |

|-----|--------|--------|-------------------|

| KEI | Return | IIOIII | Suproutine        |

| Syntax          | RET                  |                                                       |

|-----------------|----------------------|-------------------------------------------------------|

| Operands        | -                    |                                                       |

| Operation       | PC ← TOS             |                                                       |

| Status Affected | -                    |                                                       |

| OP-Code         | 00 0000 0100 0000    |                                                       |

| Description     | Return from subrouti | ne. The stack is POPed and the top of the stack       |

| ·               | (TOS) is loaded into | the program counter. This is a two-cycle instruction. |

| Cycle           | Ž ´                  |                                                       |

| Example         | RETURN               | A : PC = TOS                                          |

RLF Rotate Left f through Carry

Syntax RLF f [,d] Operands f:  $00h \sim 7Fh$ , d: 0, 1

Operation 1.001 ~ 7FII, d . 0, 1

C Register f

Status Affected C

OP-Code 00 1101 dfff ffff

Description The contents of register 'f' are rotated one bit to the left through the Carry

Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is

stored back in register 'f'.

Cycle 1

Example RLF REG1,0 B: REG1 = 1110 0110, C = 0

A: REG1 = 1110 0110 W = 1100 1100, C = 1

RRF Rotate Right f through Carry

Syntax RRF f [,d]

Operands  $f: 00h \sim 7Fh, d: 0, 1$

С

Operation C Register f

Status Affected

OP-Code 00 1100 dfff ffff

Description The contents of register 'f' are rotated one bit to the right through the

Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the

result is placed back in register 'f'.

Cycle 1

Example RRF REG1,0 B: REG1 = 1110 0110, C = 0

A: REG1 = 1110 0110

W = 0111 0011, C = 0

SLEEP Go into standby mode, Clock oscillation stops

Syntax SLEEP

Operands Operation Status Affected -

OP-Code 00 0000 1000 1010

Description Go into SLEEP mode with the oscillator stopped.

Cycle

Example SLEEP -

| SUBWF           | Subtract W from f                    |                                                                                                   |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------|

| Syntax          | SUBWF f [,d]                         |                                                                                                   |

| Operands        | f: 00h ~ 7Fh, d: 0, 1                |                                                                                                   |

| Operation       | $(destination) \leftarrow (f) - (W)$ |                                                                                                   |

| Status Affected | C, DC, Z                             |                                                                                                   |

| OP-Code         | 00 0010 dfff ffff                    |                                                                                                   |

| Description     |                                      | hod) W register from register 'f'. If 'd' is 0, gister. If 'd' is 1, the result is stored back in |

| Cycle           | 1                                    |                                                                                                   |

| Example         | SUBWF REG1,1                         | B : REG1 = 3, W = 2, C = ?, Z = ?<br>A : REG1 = 1, W = 2, C = 1, Z = 0                            |

|                 |                                      |                                                                                                   |

|                 | SUBWF REG1,1                         | B : REG1 = 2, W = 2, C = ?, Z = ?<br>A : REG1 = 0, W = 2, C = 1, Z = 1                            |

|                 | SUBWF REG1,1                         | B: REG1 = 1, W = 2, C = ?, Z = ?<br>A: REG1 = FFh, W = 2, C = 0, Z = 0                            |

|                 |                                      |                                                                                                   |

|--|

| Syntax          | SWAPF f [,d]             |                                                            |

|-----------------|--------------------------|------------------------------------------------------------|

| Operands        | f: 00h ~ 7Fh, d: 0, 1    |                                                            |

| Operation       | (destination,7~4) ← (f.3 | 3~0), (destination.3~0) ← (f.7~4)                          |

| Status Affected | <u>-</u>                 |                                                            |

| OP-Code         | 00 1110 dfff ffff        |                                                            |

| Description     |                          | bbles of register 'f' are exchanged. If 'd' is 0, the      |

|                 | result is placed in W re | gister. If 'd' is 1, the result is placed in register 'f'. |

| Cycle           | 1                        |                                                            |

| Example         | SWAPF REG, 0             | B : REG1 = 0xA5                                            |

A : REG1 = 0xA5, W = 0x5A

# TESTZ Test if 'f' is zero

|                 | 100111 1 10 2010                                            |                     |  |  |  |  |

|-----------------|-------------------------------------------------------------|---------------------|--|--|--|--|

| Syntax          | TESTZ f                                                     |                     |  |  |  |  |

| Operands        | f : 00h ~ 7Fh                                               |                     |  |  |  |  |

| Operation       | Set Z flag if (f) is 0                                      |                     |  |  |  |  |

| Status Affected | Z                                                           |                     |  |  |  |  |

| OP-Code         | 00 1000 1fff ffff                                           |                     |  |  |  |  |

| Description     | If the content of register 'f' is 0, Zero flag is set to 1. |                     |  |  |  |  |

| Cycle           | 1                                                           | -                   |  |  |  |  |

| Example         | TESTZ REG1                                                  | B: REG1 = 0, Z = ?  |  |  |  |  |

| -               |                                                             | A : REG1 = 0, Z = 1 |  |  |  |  |

| •               |                                                             | A : REG1 = 0, Z = 1 |  |  |  |  |

# XORLW Exclusive OR Literal with W

| Syntax          | XORLW k                                           |                                                                     |

|-----------------|---------------------------------------------------|---------------------------------------------------------------------|

| Operands        | k : 00h ~ FFh                                     |                                                                     |

| Operation       | $(W) \leftarrow (W) XOR k$                        |                                                                     |

| Status Affected | Ż                                                 |                                                                     |

| OP-Code         | 01 1111 kkkk kkkk                                 |                                                                     |

| Description     | The contents of the W r result is placed in the W | egister are XOR'ed with the eight-bit literal 'k'. The<br>register. |

| Cycle           | 1                                                 | •                                                                   |

| Example         | XORLW 0xAF                                        | B:W=0xB5                                                            |

|                 |                                                   | A:W=0x1A                                                            |

| XORWF           | Exclusive OR W wi      | th f                                                                                                          |

|-----------------|------------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax          | XORWF f [,d]           |                                                                                                               |

| Operands        | f: 00h ~ 7Fh, d: 0, 1  |                                                                                                               |

| Operation       | (destination) ← (W) XO | R (f)                                                                                                         |

| Status Affected | Z                      |                                                                                                               |

| OP-Code         | 00 0110 dfff ffff      |                                                                                                               |

| Description     |                        | nts of the W register with register 'f'. If 'd' is 0, the register. If 'd' is 1, the result is stored back in |

| Cycle           | 1                      |                                                                                                               |

| Example         | XORWF REG 1            | B : REG = $0xAF$ , W = $0xB5$                                                                                 |

|                 |                        | A : REG = $0x1A$ , W = $0xB5$                                                                                 |

# 2. Control Register

| Description                           | Mnemonic | Dec | Hex  | R/W |

|---------------------------------------|----------|-----|------|-----|

| System Config Reg Low                 | SYSL     | -   | 2000 | -   |

| Indirect File Reg                     | INDF     | 0   | 00H  | -   |

| Timer 0 Counter Reg                   | T0CNT    | 1   | 01H  | R   |

| Program Counter Low                   | PCL      | 2   | 02H  | R/W |

| System Flags Reg                      | STATUS   | 3   | 03H  | R/W |

| File Select Reg                       | FSR      | 4   | 04H  | R/W |

| Port A Data Reg                       | PAD      | 5   | 05H  | R/W |

| Port B Data Reg                       | PBD      | 6   | 06H  | R/W |

| Port C Data Reg                       | PCD      | 7   | 07H  | R/W |

| Clock control Reg                     | CLKCON   | 8   | 08H  | R/W |

| WatchDog Timer Control Reg            | WDTE     | 9   | 09H  | -   |

| Stop mode Control Reg                 | PWRDN    | 10  | 0AH  | _   |