TMU3102 USB Controller

### **GENERAL DESCRIPTION**

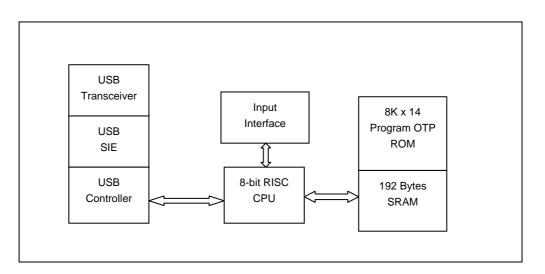

The TMU3102 is an 8-bit microprocessor embedded device tailored to the USB general purpose application. It includes an 8-bit RISC CPU core, 192-byte SRAM, Low Speed USB Interface and an 8K x 14 internal program OTP-ROM.

### FEATURE

- Compliance with the Universal Serial Bus specification v1.1

- Built-in USB Transceiver without external pull-up resister and 3.3V regulator

- Support USB Suspend and Resume function

- One Control IN/OUT and one Interrupt IN endpoints

- PS2 compatible mouse interface share with USB interface

- 192 byte internal SRAM

- 8K x 14 internal program OTP-ROM.

- 8-bit RISC CPU core with only 36 instruction

- Internal Oscillator 6MHz±1.5% operation without external components.

- 3MHz instruction rate with 6MHz crystal oscillation.

- Support internal wake up timer for power saving.

- 18/20/24 pin PDIP/SOP package

### **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Name                | I/O | Description                                                                             |

|---------------------|-----|-----------------------------------------------------------------------------------------|

| VDD                 | Р   | 5V Power from USB cable                                                                 |

| VSS                 | Ρ   | Ground                                                                                  |

| X1                  |     | Test/OTP mode clock in                                                                  |

| RC6M                | 0   | Internal clock output (6MHz)                                                            |

| VPP                 |     | OTP programming power                                                                   |

| V33                 | 0   | 3.3V regulator output                                                                   |

| DP/PB[3]            | I/O | USB positive data signal / General purpose I/O (pseudo open-drain)                      |

| DM/PB[2]            | I/O | USB negative data signal / General purpose I/O (pseudo open-drain)                      |

| PB[1:0]/<br>PB[7:4] | I/O | General purpose I/O (pseudo open-drain)                                                 |

| PD[7:0]             | I/O | Multi-function I/O (pseudo open-drain, Push-pull output, Input from pin or comparator.) |

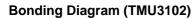

### **PIN ASSIGNMENT**

| PD[0] [ 1<br>PD[1] [ 2<br>PD[2] [ 3<br>PD[3] [ 4<br>PB[0] [ 5<br>VSS [ 6<br>VPP [ 7<br>V33 [ 8<br>X1 [ 9                                          | TMU3102<br>18 pin | 18 PD[4]<br>17 PD[5]<br>16 PD[6]<br>15 PD[7]<br>14 PB[1]<br>13 DP/PB[3]<br>12 DM/PB[2]<br>11 VDD<br>10 RC6M                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PD[0] [ 1<br>PD[1] [ 2<br>PD[2] [ 3<br>PD[3] [ 4<br>PB[4] [ 5<br>PB[0] [ 6<br>VSS [ 7<br>VPP [ 8<br>V33 [ 9<br>X1 [ 10                            | TMU3102<br>20 pin | 20 PD[4]<br>19 PD[5]<br>18 PD[6]<br>17 PD[7]<br>16 PB[1]<br>15 PB[5]<br>14 DP/PB[3]<br>13 DM/PB[2]<br>12 VDD<br>11 RC6M                        |

| PD[0] [ 1<br>PD[1] [ 2<br>PD[2] [ 3<br>PD[3] [ 4<br>PB[4] [ 5<br>PB[6] [ 6<br>PB[0] [ 7<br>N.C. [ 8<br>VSS [ 9<br>VPP [ 10<br>V33 [ 11<br>X1 [ 12 | TMU3102<br>24 pin | 24 PD[4]<br>23 PD[5]<br>22 PD[6]<br>21 PD[7]<br>20 PB[1]<br>19 PB[5]<br>18 PB[7]<br>17 N.C.<br>16 DP/PB[3]<br>15 DM/PB[2]<br>14 VDD<br>13 RC6M |

#### FUNCTIONAL DESCRIPTION

### 1. CPU Core

#### 1.1 Clock Scheme and Instruction Cycle

The clock input (X1) is internally divided by two to generate Q1 state and Q2 state for each instruction cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program ROM and latched into the instruction register in Q2. It is then decoded and executed during the following Q1-Q2 cycle. **1.2** Programming Counter (PC) and Stack

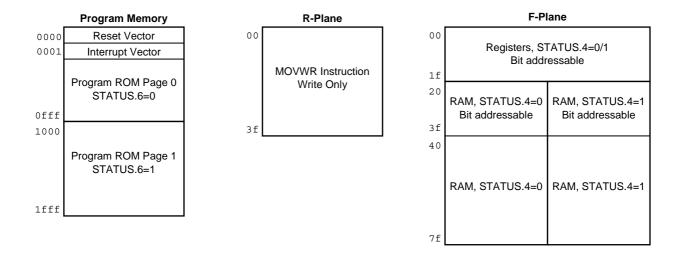

The Programming Counter is 13-bit wide capable of addressing a 8K x 14 program ROM. As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC value is normally increased by one except the followings. The Reset Vector (0) and the Interrupt Vector (1) are provided for PC initialization. For CALL/GOTO instructions, PC loads its lower 12 bits from instruction word and the MSB from STATUS's bit 6. For RET/RETI/RETLW instructions, PC retrieves its content from the top level STACK. For the other instructions updating PC[7:0], the PC[12:8] keeps unchanged.

The STACK is 13-bit wide and 6-level in depth. The CALL instruction and Hardware interrupt will push STACK level in order, While the RET/RETI/RETLW instruction pops the STACK level in order.

#### 1.3 Addressing Mode

There are two Data Memory Plane in CPU, R-Plane and F-Plane. The registers in R-Plane are write-only. The "MOVWR" instruction copy the W-register's content to those registers by direct addressing mode. Registers in F-Plane can be addressed directly or indirectly. Indirect Addressing is made by address "0", where FSR points to an actual address. The first half of F-Plane is also bit-addressable.

### **<u>1.4</u>** ALU and Working (W) Register

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. In two-operand instructions, typically one operand is the W register, which is an 8-bit non-addressable register used for ALU operations. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either W register or a file register.

Depending on the instruction executed, the ALU may affect the values of Carry(C), Digit Carry(DC), and Zero(Z) Flags in the STATUS register. The C and DC flags operate as a /Borrow and /Digit Borrow, respectively, in subtraction.

### 1.5 STATUS Register

This register contains the arithmetic status of ALU and the page select for Program ROM and Data RAM. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect those bits.

### 1.6 Interrupt

Each interrupt source has its own enable control bit. An interrupt event will set its individual flag. If the corresponding interrupt enable bit has been set, it would trigger CPU to service the interrupt. CPU accepts interrupt in the end of current executed instruction cycle. In the mean while, A "CALL 0001" instruction is inserted to CPU, and the I-flag is set to prevent recursive interrupt nesting. The I-flag is cleared in the instruction after the "RETI" instruction. That is, at least one instruction in main program is executed before service the pending interrupt. The interrupt event is level trigged. F/W must clear the interrupt event register while serves the interrupt routine.

#### 1.7 Instruction Set

Each instruction is a 14-bit word divided into an OPCODE, which specified the instruction type, and one or more operands, which further specify the operation of the instruction. The instructions can be categorized as byte-oriented, bit-oriented and literal operations list in the following table.

For byte-oriented instructions, "f" represents address designator and "d" represents destination designator. The address designator is used to specify which address in F-Plane is to be used by the instruction. The destination designator specifies where the result of the operation is to be placed. If "d" is "0", the result is placed in the W register. If "d" is "1", the result is placed in the address specified in the instruction.

For bit-oriented instructions, "b" represents a bit field designator, which selects the number of the bit affected by the operation, while "f" represents the address designator.

For literal operations, "k" represents the literal or constant value.

For "MOVWR" instruction, "r" specifies which address in R-Plane is to be used by the instruction.

All instructions are single cycle except for program branches, which are two-cycle.

| Mnemonic   | Op Code           | Cycles | Flag<br>Affect | Description                                   |

|------------|-------------------|--------|----------------|-----------------------------------------------|

| NOP        | 00 0000 0 0000000 | 1      | -              | No operation                                  |

| SLEEP      | 00 0000 0 0000011 | 1      |                | Go into standby mode, Clock oscillation stops |

| CLRWDT     | 00 0000 0 0000100 | 1      |                | Clear and enable Watch Dog Timer              |

| MOVWR r    | 00 0000 0 0rrrrrr | 1      | -              | Move W to "r"                                 |

| RET        | 00 0000 0 1000000 | 2      | -              | Return                                        |

| RETI       | 00 0000 0 1100000 | 2      | -              | Return from interrupt                         |

| MOVWF f    | 00 0000 1 fffffff | 1      | -              | Move W to "f"                                 |

| CLRW       | 00 0001 0 1000000 | 1      | Z              | Clear W                                       |

| CLRF f     | 00 0001 1 fffffff | 1      | Z              | Clear "f"                                     |

| SUBWF f,d  | 00 0010 d fffffff | 1      | C,DC,Z         | Subtract W from "f"                           |

| DECF f,d   | 00 0011 d fffffff | 1      | Z              | Decrement "f"                                 |

| IORWF f,d  | 00 0100 d fffffff | 1      | Z              | OR W with "f"                                 |

| ANDWF f,d  | 00 0101 d fffffff | 1      | Z              | AND W with "f"                                |

| XORWF f,d  | 00 0110 d fffffff | 1      | Z              | XOR W with "f"                                |

| ADDWF f,d  | 00 0111 d fffffff | 1      | C,DC,Z         | Add W and "f"                                 |

| MOVFW f    | 00 1000 0 fffffff | 1      | -              | Move "f" to "w"                               |

| TESTZ f    | 00 1000 1 fffffff | 1      | Z              | Test if "f" is zero                           |

| COMF f,d   | 00 1001 d fffffff | 1      | Z              | Complement "f"                                |

| INCF f,d   | 00 1010 d fffffff | 1      | Z              | Increment "f"                                 |

| DECFSZ f,d | 00 1011 d fffffff | 1 or 2 | -              | Decrement "f", skip if zero                   |

| RRF f,d    | 00 1100 d fffffff | 1      | С              | Rotate right "f" through carry                |

| RLF f,d    | 00 1101 d fffffff | 1      | С              | Rotate left "f" through carry                 |

| SWAPF f,d  | 00 1110 d fffffff | 1      | -              | Swap high/low nibble of "f"                   |

| INCFSZ f,d | 00 1111 d fffffff | 1 or 2 | -              | Increment "f", skip if zero                   |

| BCF f,b    | 010 00 bbb ffffff | 1      | -              | Clear "b" bit of "f"                          |

| BSF f,b    | 010 01 bbb ffffff | 1      | -              | Set "b" bit of "f"                            |

| BTFSC f,b  | 010 10 bbb ffffff | 1 or 2 | -              | Test "b" bit of "f", skip if clear            |

| BTFSS f,b  | 010 11 bbb ffffff | 1 or 2 | -              | Test "b" bit of "f", skip if set              |

| RETLW k    | 011 000 kkkkkkkk  | 2      | -              | Return, place Literal "k" in W                |

| MOVLW k    | 011 001 kkkkkkkk  | 1      | -              | Move Literal "k" to W                         |

| IORLW k    | 011 010 kkkkkkkk  | 1      | Z              | OR Literal "k" with W                         |

| ANDLW k    | 011 011 kkkkkkkk  | 1      | Z              | AND Literal "k" with W                        |

| ADDLW k    | 011 100 kkkkkkkk  | 1      | C,DC,Z         | Add Literal "k" to W                          |

| XORLW k    | 011 111 kkkkkkkk  | 1      | Z              | XOR Literal "k" with W                        |

| CALL k     | 10 kkkk kkkkkkkk  | 2      | -              | Call subroutine "k"                           |

| GOTO k     | 11 kkkk kkkkkkk   | 2      | -              | Jump to branch "k"                            |

# 2. I/O Port

## 2.1 PB[1:0]/PB[7:4]

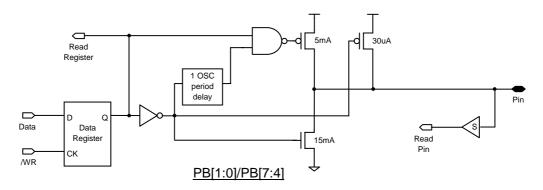

These pins are "Pseudo-Open-Drain" structure. In "Read-Modify-Write" instruction, CPU actually reads the output data register. In the others instructions, CPU reads the pin data. The so-called "Read-Modify-Write" instruction includes BSF, BCF and all instructions using F-Plane as destination. The PB[0] pin can also generate interrupt (PB0int) at its falling edge.

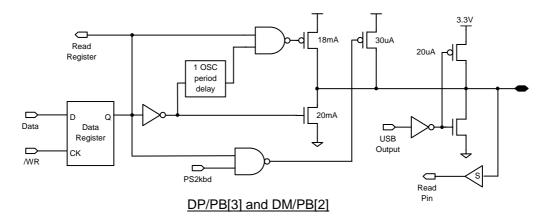

## 2.2 DP/PB[3] and DM/PB[2]

These pins are similar to PB[1:0], except they share the pin with USB function. An extra control bit "PS2kbd" is used to enable the small pull-up current.

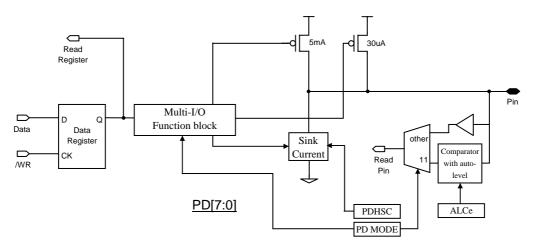

# 2.3 PD[7:0]

The attributions of I/O pins are defined to be multi-function for adapting different application. The PD MODE defines the I/O type as below. If is "pseudo open drain" structure, the function are similar to PB, only different is sink capability, the sink capability of pin can be control form corresponding PDHSC register. The read path can be read from output data latch or pin data. About the comparator with auto-level function is very suitable for mouse application, PD[0]/PD[1] must be grouped to mapping X1/X2 or Y1/Y2, PD[2]/PD[3] also must mapping the rest axis. When PD[3:0] operating on comparator with auto level function, this ALCe register must be set, clear ALCe register to disable this function for saving power.

| PD[7:0] I/O type            | PD MODE | 0         | Dutput                | Read                 | Note                                     |  |

|-----------------------------|---------|-----------|-----------------------|----------------------|------------------------------------------|--|

|                             |         | HIGH      | LOW                   |                      |                                          |  |

| Pseudo open drain           | 00      | 5mA->30uA | PDHSC=0, Low<br>Sink  |                      | PD[5:0]: Low sink=8mA,<br>High sink=30mA |  |

| Push-pull output            | 01      | 5mA       | PDHSC=1, High<br>Sink | Output data register | PD[7:6]: Low sink=16mA<br>High sink=50mA |  |

| Input, read from pin        | 10      | N.A.      | N.A.                  | Pin data             |                                          |  |

| Input, read from comparator | 11      | N.A       | N.A.                  | Pin data             | PD[7:4] unavailable                      |  |

### 3. Power Down Mode

The power down mode is activated by SLEEP instruction. In power down mode, the crystal clock oscillation stops to minimize power consumption. Power down mode can be terminated by Reset or enabled Interrupts.

#### 4. Watch Dog Timer

The Watch Dog Timer (WDT) is disabled after Reset. F/W can use the CLRWDT instruction to clear and enable the Watch Dog Timer. Once enabled, the Watch Dog Timer overflow and generate a chip reset signal if no CLRWDT executed in a period of 4000000 oscillator's cycle (0.66 second for 6MHz crystal). The WDT does not work in Power Down Mode to provide wake-up function. It is only designed to prevent F/W goes into endless loop.

### 5. Timer 0

The Timer 0 is an 8-bit wide register of F-Plane. It can be read or written as any other register of F-Plane. Besides, Timer 0 increases itself periodically and reloads itself with a special value every time while roll over. The value to be load at roll over point is defined by "Timer 0 Reload" (T0RLD) register in the R-Plane. The period which Timer 0 increases itself is defined by "Timer 0 Pre-Scale" (T0PSCL) register in R-Plane, the default (0) mean 4 instruction cycles increase Timer 0. The Timer 0 also generates interrupt (T0int) while it rolls over.

### 6. Internal Wakeup Timer

Tx1615 is built-in a nonstop internal RC oscillator whose period is around 50ms. It may be used for periodic polling Tx1615 on mouse application. While enter power down mode, crystal clock oscillation is stop. If enable the WKT interrupt, when wakeup timer overflow will generate wakeup interrupt and WKTint=1. Write any to CLRWKT register can clear this wakeup timer.

### 7. Internal Oscillator Operation

After power-on, the internal oscillator will provide 6MHz±10% frequency. On USB mode, if set EN\_USB=1, the frequency will automatically tune to 6MHz±1.5% according the USB bus traffic. When sleep mode occurs, the internal oscillator is stopping and RC6M is keep high.

## 8. USB Engine

The USB engine includes the Serial Interface Engine (SIE), the low-speed USB I/O transceiver and the 3.3 Volt Regulator. The SIE block performs most of the USB interface function with only minimum support from F/W. Three endpoints are supported. Endpoint 0 is used to receive and transmit control (including SETUP) packets while Endpoint 1 is only used to transmit data packets.

The USB SIE handles the following USB bus activity independently:

- 1. Bitstuffing/unstuffing

- 2. CRC generation/checking

- 3. ACK/NAK

- 4. TOKEN type identification

- 5. Address checking

F/W handles the following tasks:

- 1. Coordinate enumeration by responding to SETUP packets

- 2. Fill and empty the FIFOs

- 3. Suspend/Resume coordination

- 4. Verify and select DATA toggle values

## 8.1 USB Device Address

The USB device address register (USBadr) stores the device's address. This register is reset to all 0 after chip reset. F/W must write this register a valid value after the USB enumeration process.

#### 8.2 Endpoint 0 receive

After receiving a packet and placing the data into the Endpoint 0 receive FIFO (RC0FIFO), TX1615 updates the Endpoint 0 status registers to record the receive status and then generates an Endpoint 0 receive interrupt (RC0int). F/W can read the status register for the recent transfer information, which includes the

data byte count (RC0cnt), data direction (EP0dir), SETUP token flag (EP0set), packet toggle (RC0tgl) and data valid flag (RC0err). The received data is always stored into RC0FIFO and the RC0cnt is always updated for DATA packets following SETUP tokens. The data following an OUT token is written into the RC0FIFO, and the RC0cnt is updated unless Endpoint 0 STALL (EP0stall) is set or Endpoint 0 receive ready (RC0rdy) is cleared. The SIE clears the RC0rdy automatically and generates RC0int interrupt when the RC0cnt or RC0FIFO is updated. As long as the RC0rdy is cleared, SIE keep responding NAK to Host's Endpoint 0 OUT packet request. F/W should set the RC0rdy flag after the RC0int interrupt is asserted and RC0FIFO is read out.

## 8.3 Endpoint 0 transmit

After detecting a valid Endpoint 0 IN token, TX1615 automatically transmit the data pre-stored in the Endpoint 0 transmit FIFO (TX0FIFO) to the USB bus if the Endpoint 0 transmit ready flag (TX0rdy) is set and the EP0stall is cleared. The number of byte to be transmitted depends on the Endpoint 0 transmit byte count register (TX0cnt). The DATA0/1 token to be transmitted depends on the Endpoint 0 transmit toggle control bit (TX0tgl). After the TX0FIFO is updated, TX0rdy should be set to 1. This enables the TX1615 to respond to an Endpoint 0 IN packet. TX0rdy is cleared and an Endpoint 0 transmit interrupt (TX0int) is generated once the USB host acknowledges the data transmission. The interrupt service routine can check TX0rdy to confirm that the data transfer was successful.

## 8.4 Endpoint 1 transmit

Endpoint1 is capable of transmit only. These endpoints are enabled when the Endpoint1 configuration control bit (EP1cfg) is set. After detecting a valid Endpoint 1 IN token, TX1615 automatically transmit the data pre-stored in the Endpoint 1 transmit FIFO (TX1FIFO) to the USB bus if the Endpoint 1 transmit ready flag (TX1rdy) is set and the EP1stall is cleared. The number of byte to be transmitted depends on the Endpoint 1 transmit toggle control bit (TX1tgl). After the TX1FIFO is updated, TX1rdy should be set to 1. This enables the TX1615 to respond to an Endpoint 1 IN packet. TX1rdy is cleared and an Endpoint 1 transmit interrupt (TX1int) is generated once the USB host acknowledges the data transmission. The interrupt service routine can check TX1rdy to confirm that the data transfer was successful.

## 8.5 USB Control and Status

Other USB control bits include the USB enable (ENUSB), Suspend (Susp), Resume output (RsmO), Control Read (CtrRD), and corresponding interrupt enable bits. The CtrRD should be set when program detects the current transfer is an Endpoint0 Control Read Transfer. Once this bit is set, the TX1615 will stall an Endpoint0 OUT packet with DATA toggle 0 or byte count other than 0. Other USB status flag includes the USB reset interrupt (RSTint), Resume input interrupt (RSMint), and USB Suspend interrupt (SUSPint).

## 8.6 Suspend and Resume

Once the Suspend condition is asserted, F/W can set the Susp bit to save the power consumption of USB Engine. F/W can further save the device power by force the CPU to go into the Power Down Mode. In the Power Down mode, the X'tal is stop, but CPU can be waken-up by the trigger of enabled interrupt's source, which includes RSMint, KBDint and PB0int.

The TX1615 send Resume signaling to USB bus when Susp=1 and RsmO=1. In the suspend mode, if a valid interrupt is asserted, F/W should send resume signal to wake up the USB bus.

Some PCs send Reset wakeup instead of Resume under Suspend condition, TX1615 will first service RSMint, at the same time RSTint flag is set after several clocks.

# 8.7 Interrupt flags

Perform byte operation (movwf, andwf, xorwf...) to clear interrupt flags for F-plane 0x11, 0x12. Write 0 to clear mapping interrupt flag, if write 1 don't affect mapping interrupt flag status. Avoid using bit clear(BCF) to clear interrupt flags.

### **MEMORY MAP of F-Plane**

| Name             | Address      | R/W        | Rst    | Description                                                                                     |

|------------------|--------------|------------|--------|-------------------------------------------------------------------------------------------------|

| IndF             | 00.7~0       | -          | -      | Indirect Register                                                                               |

| Timer0           | 01.7~0       | R/W        | 0      | Timer 0                                                                                         |

| PCL              | 02.7~0       | R/W        | 0      | Program Counter [7~0]                                                                           |

| ROMpage          | 03.6         | R/W        | 0      | Program ROM Page Select (STATUS.6)                                                              |

| RAMbank          | 03.4         | R/W        | 0      | SRAM Bank Select (STATUS.4)                                                                     |

| Z                | 03.2         | R/W        | 0      | Zero Flag (STATUS.2)                                                                            |

| DC               | 03.1         | R/W        | 0      | Decimal Carry Flag or Decimal /Borrow Flag (STATUS.1)                                           |

| С                | 03.0         | R/W        | 0      | Carry Flag or /Borrow Flag (STATUS.0)                                                           |

| FSR              | 04.6~0       | R/W        | 0      | File Select Register to define Address in indirect addressing mode                              |

| PBD              | 06.7~0       | R/W        | ff     | Port B output datalatch / pin                                                                   |

| PDD              | 0D.7~0       | R/W        | ff     | Port D output datalatch / pin / comparator dataindata                                           |

| GPR0             | 0E.7~0       | R/W        | -      | General Purpose Register 0                                                                      |

| GPR1             | 0F.7~0       | R/W        | -      | General Purpose Register 1                                                                      |

| ENUSB            | 10.7         | R/W        | 0      | USB function enable (1)                                                                         |

| USBadr           | 10.6~0       | R/W        | 0      | USB device address                                                                              |

| RC0int           | 11.7         | R/W        | 0      | Endpoint 0 Receive Interrupt flag, write 0 to clear flag.                                       |

| TX0int           | 11.6         | R/W        | 0      | Endpoint 0 Transmit Interrupt flag, write 0 to clear flag.                                      |

| TX1int           | 11.5         | R/W        | 0      | Endpoint 1 Transmit Interrupt flag, write 0 to clear flag.                                      |

| RSTint           | 11.3         | R/W        | 0      | USB Bus Reset Interrupt flag, write 0 to clear flag.                                            |

| SUSPint          | 11.2         | R/W        | 0      | USB Suspend Interrupt flag, write 0 to clear flag.                                              |

| WKTint           | 11.1         | R/W        | 0      | Wake-up timer (50ms) Interrupt flag, write 0 to clear flag.                                     |

| RSMint<br>PB0int | 12.3<br>12.1 | R/W<br>R/W | 0<br>0 | USB Resume Interrupt flag, write 0 to clear flag.<br>PB0 interrupt flag, write 0 to clear flag. |

| T0int            | 12.1         | R/W        | 0      | Timer0 Interrupt flag, write 0 to clear flag.                                                   |

| Susp             | 13.7         | R/W        | 0      | F/W force USB interface to go into suspend mode.                                                |

| RsmO             | 13.6         | R/W        | Ő      | F/W force USB interface send Resume signal in suspend mode.                                     |

| EP1cfg           | 13.5         | R/W        | õ      | Set Endpoint 1 configuration.                                                                   |

| CtrRD            | 13.3         | R/W        | Õ      | H/W will stall an invalid OUT token during Control Read transfer.                               |

| RC0rdy           | 13.0         | R/W        | Õ      | Endpoint 0 ready for receive, clear by H/W while RC0int occurs.                                 |

| RC0tgl           | 14.7         | R          |        | 1: received DATA1 packet; 0: received DATA0 Packet.                                             |

| RC0err           | 14.6         | R          |        | Endpoint 0 received data error.                                                                 |

| EP0dir           | 14.5         | R          |        | 1: IN transfer; 0: OUT/SETUP transfer.                                                          |

| EP0set           | 14.4         | R          |        | SETUP Token indicator.                                                                          |

| RC0cnt           | 14.3~0       | R          |        | Received data byte count.                                                                       |

| TX0rdy           | 15.7         | R/W        | 0      | Endpoint 0 ready for transmit, clear by H/W while TX0int occurs.                                |

| TX0tgl           | 15.6         | R/W        | 0      | Endpoint 0 transmit DATA1/DATA0 packet.                                                         |

| EP0stall         | 15.5         | R/W        | 0      | Endpoint 0 will stall OUT/IN packet while this bit is 1.                                        |

| TX0cnt           | 15.3~0       | R/W        | 0      | Endpoint 0 transmit byte count.                                                                 |

| TX1rdy           | 16.7         | R/W        | 0      | Endpoint 1 ready for transmit, clear by H/W while TX1int occurs.                                |

| TX1tgl           | 16.6         | R/W        | 0      | Endpoint 1 transmit DATA1/DATA0 packet.                                                         |

| EP1stall         | 16.5         | R/W        | 0      | Endpoint 1 will stall IN packet while this bit is 1.                                            |

| TX1cnt           | 16.3~0       | R/W        | 0      | Endpoint 1 transmit byte count.                                                                 |

| <b>RC0FIFO</b>   | 18~1F        | R          |        | Endpoint 0 Receive Buffer (8 Bytes)                                                             |

| SRAM             | 20~7F        | R/W        | -      | Internal RAM (96 Bytes x 2 Banks)                                                               |

### **MEMORY MAP of R-Plane**

| TORLD01.7~0W0Timer0 overflow reload valueTOPSCL02.3~0W0Timer0 Pre-Scale, 0:divided by 2, 1:divided by 4, 7:divided by 256, 8:c<br>Time base is 2xinstruction cycles.PWRdwn03W0Write this register to enter Power-Down ModeWDTe04W0Write this register to clear WDT and enable WDTCLRWKT08W0Write this register to clear Wake-up TimerPDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PD7MODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin |                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Time base is 2xinstruction cycles.PWRdwn03W0Write this register to enter Power-Down ModeWDTe04W0Write this register to clear WDT and enable WDTCLRWKT08W0Write this register to clear Wake-up TimerPDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PDTMODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                        |                |

| PWRdwn03W0Write this register to enter Power-Down ModeWDTe04W0Write this register to clear WDT and enable WDTCLRWKT08W0Write this register to clear Wake-up TimerPDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PDTMODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                          | 3mA            |

| WDTe04W0Write this register to clear WDT and enable WDTCLRWKT08W0Write this register to clear Wake-up TimerPDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PDTMODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                | <u>3mA</u>     |

| CLRWKT08W0Write this register to clear Wake-up TimerPDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PD7MODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                       | 3mA            |

| PDHSC0E.7~0W0Port D pin in High sink current mode, PD[7:6]:4mA/50mA, PD[5:0]:2mA/8PD7MODE0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                                                                           | 8mA            |

| PD7MODE 0D.7~6W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD6MODE 0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE 0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE 0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                                                                                                                                                         | 8mA            |

| PD6MODE 0D.5~4W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD5MODE 0D.3~2W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pinPD4MODE 0D.1~0W000:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| PD5MODE 0D.3~2 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin   PD4MODE 0D.1~0 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| PD4MODE 0D.1~0 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| PD3MODE 0C.7~6 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin, 11:input fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rom comparator |

| PD2MODE 0C.5~4 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin, 11:input fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rom comparator |

| PD1MODE 0C.3~2 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin, 11:input fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rom comparator |

| PD0MODE 0C.1~0 W 0 00:Pseudo open-drain, 01:Push-Pull output, 10:input from pin, 11:input fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rom comparator |

| TESTreg 0F.3~0 W 0 Test Mode control, keep 0 in normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| TX0FIFO 18~1F W - Endpoint 0 Transmit Buffer (8 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| TX1FIFO 20~27 W - Endpoint 1 Transmit Buffer (8 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| RC0ie 11.7 W 0 RC0 Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| TX0ie 11.6 W 0 TX0 Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| TX1ie 11.5 W 0 TX1 Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| RSTie 11.3 W 0 USB Reset Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| SUSPie 11.2 W 0 Suspend Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| WKTie 11.1 W 0 WKT Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| ALCe 12.5 W 0 Auto Level control enable(1:enable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| PS2kbd 12.4 W 0 Select PS2 Mode (1:PS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| RSMie 12.3 W 0 RSM Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| PB0ie 12.1 W 0 PB[0] Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| T0ie 12.0 W 0 Timer 0 Interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

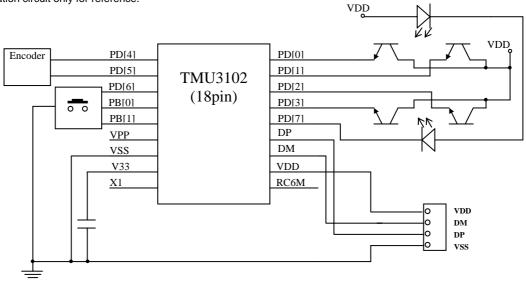

## **APPLICATION CIRCUIT**

Mouse application circuit only for reference.

## ABSOLOUTE MAXIMUM RATINGS

GND= 0V

| Name                          | Symbol | Range           | Unit |

|-------------------------------|--------|-----------------|------|

| Maximum Supply Voltage        | VDD    | -0.3 to 5.5     | V    |

| Maximum Input Voltage         | Vin    | -0.3 to VDD+0.3 | V    |

| Maximum output Voltage        | Vout   | -0.3 to VDD+0.3 | V    |

| Maximum Operating Temperature | Topg   | -5 to +70       |      |

| Maximum Storage Temperature   | Tstg   | -25 to +125     |      |

### **RECOMMEND OPERATING CONDITION**

at Ta=-20 to 70 ,GND= 0V

| Name              | Symb. | Min. | Max. | Unit |

|-------------------|-------|------|------|------|

| Supply Voltage    | VDD   | 4.5  | 5.5  | V    |

| Input "H" Voltage | Vih   | 3.5  | 5.5  | V    |

| Input "L" Voltage | Vil1  | 0    | 0.8  | V    |

### DC ELECTRICAL CHARACTERISTICS:

at Ta=25 ,VDD=5.0V, VSS= 0V,

| , ,                      | · · · |      | _    |      |      |           |                   |

|--------------------------|-------|------|------|------|------|-----------|-------------------|

| Name                     | Symb. | Min. | Тур. | Max. | Unit | Condition | Note              |

| Operating current        | lcc   |      | 10   |      | mA   | Fosc=6MHz | No load           |

| Internal clock frequence | Fosc1 | 4    |      | 8    | MHz  |           |                   |

|                          | Fosc2 | 5.91 | 6.0  | 6.09 | MHz  | USB Mode  |                   |

| Suspend current          | Isus  |      | 360  |      | uA   |           |                   |

| PB Output High Voltage   | Vboh1 |      | 4.5  |      | V    | loh=5mA   |                   |

|                          | Vboh2 |      | 4.0  |      | V    | loh=30uA  |                   |

|                          | Vboh3 |      | 4.5  |      | V    | loh=18mA  | PB[3:2](PS2 mode) |

| PB Output Low Voltage    | Vbol1 |      | 0.4  |      | V    | lol=15mA  |                   |

| -                        | Vbol2 |      | 0.4  |      | V    | lol=20mA  | PB[3:2](PS2 mode) |

| PB Input High Voltage    | Vbih  | 1.8  |      |      | V    |           |                   |

| PD Output High Voltage   | Vdoh1 |      | 4.5  |      | V    | loh=5mA   | PD push-pull      |

|                          | Vdoh2 |      | 4.0  |      | V    | Ioh=30uA  |                   |

| PD Output Low voltage    | Vdol1 |      | 0.4  |      | V    | lol=8mA   | PD[5:0] low sink  |

|                          | Vdol2 |      | 0.4  |      | V    | lol=16mA  | PD[7:6] low sink  |

|                          | Vdol3 |      | 0.4  |      | V    | Iol=30mA  | PD[5:0] high sink |

|                          | Vdol4 |      | 0.4  |      | V    | lol=50mA  | PD[7:6] high sink |

| PD Input High Voltage    | Vdih  | 2.5  |      |      | V    |           |                   |

| Low Voltage Detector     | Vlvdt |      | 3.0  |      | V    |           |                   |

### USB TIMING / ELECTRICAL CHARACTERISTICS:

At Ta=25 ,VDD=5.0V, VSS= 0V, Fosc=6MHz

| Name                           | Symb. | Min.  | Max.  | Unit | Note                  |  |  |

|--------------------------------|-------|-------|-------|------|-----------------------|--|--|

| DP/DM rising time              | Trise | 75    | 300   | ns   | C <sub>L</sub> =390pF |  |  |

| DP/DM falling time             | Tfall | 75    | 300   | ns   | C <sub>L</sub> =390pF |  |  |

| DP,DM cross point              | Vx    | 1.3   | 2.0   | V    |                       |  |  |

| V33 output voltage             | Vreg  | 3.2   | 3.4   | V    |                       |  |  |

| DM internal pull-high resistor |       | 1.425 | 1.575 | Kohm |                       |  |  |

|                                |       |       |       |      |                       |  |  |

Note: All USB transceiver characteristics can meet USB1.1 spec.

## **Package Information**

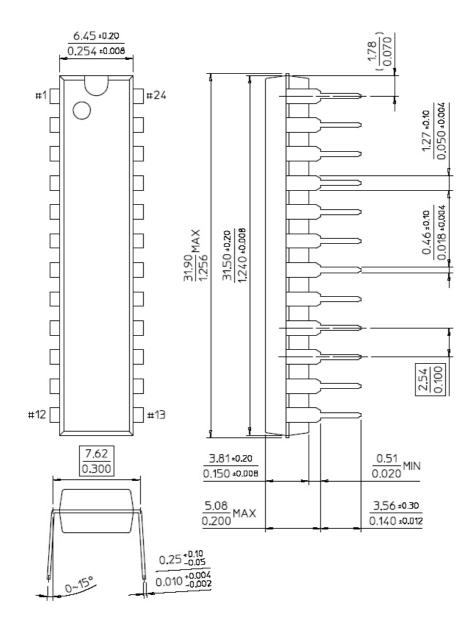

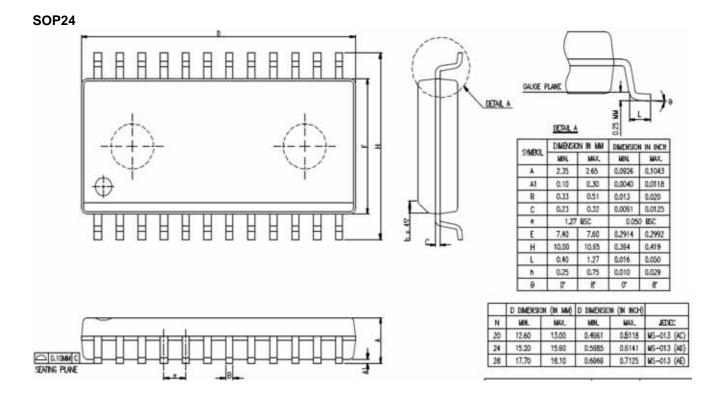

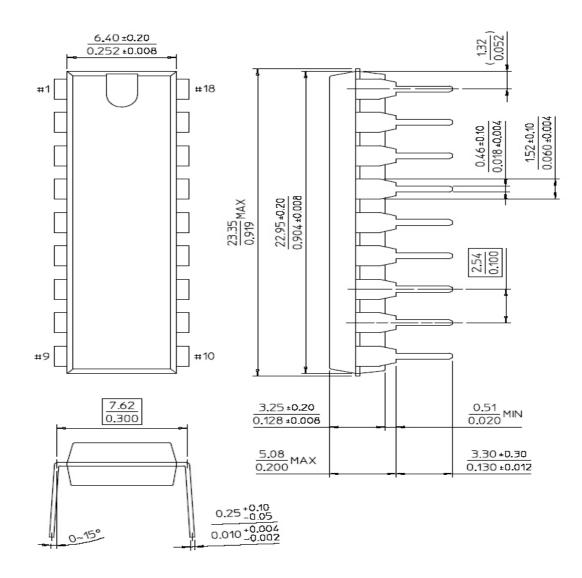

## DIP18

Dimensions in Milimeters/inches

Dimensions in Milimeters/inches

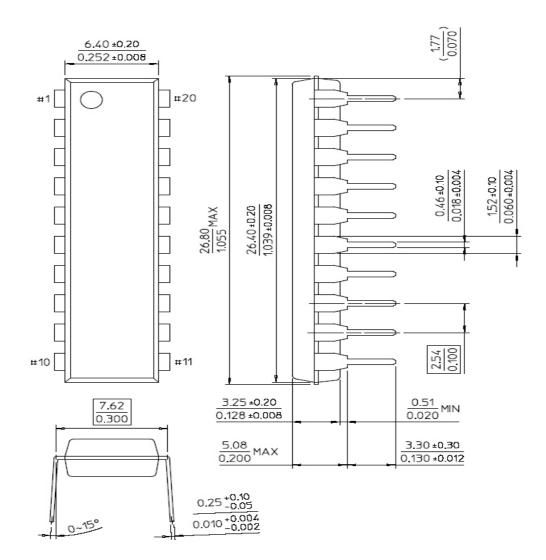

DIP20

## DIP24